ジーニックの強み

ワンストップ体制 ONE STOP

お客様のご要望をヒアリングし、仕様検討から設計~試作~評価検証~量産までの工程全般をワンストップでサポートいたします。

小ロットから大量生産まで対応可。お気軽にご相談ください。

開発・量産工程における全ての設計業務を自社リソースで対応

開発工程で必要な「基板開発」「FPGA開発」「ソフトウェア開発」「筐体開発」を全て自社リソースとして持っていることがジーニックの最大の強みです。

メンバー間の相互連携により、量産時に考慮すべき問題点を早期にフィードバックすることが可能です。

- 基板開発

- 回路設計/アートワーク~試作~評価~量産

- FPGA開発

- RTL設計、高位合成

- ソフトウェア開発

- 組込み制御(ファームウェア)、ハードウェア検査ソフト

- 筐体開発

- 構造設計~試作~評価~量産

信頼性試験や量産にも対応

私たちはオプテックスグループの一員です。ネットワークを活用し、信頼性試験の実施、量産対応工場との連携で安定・安心の製品供給をサポートいたします。

工場は国内外合わせて計4箇所ございます。車載部品についても、IATF16949認証工場にて10年以上の生産実績がございます。

窓口一本化でスムーズなやり取りが可能

複数担当者とのやり取りが不要になり、より効率の良い商談が行えます。

また、お客様の管理工数を減らせますので製造コストの大幅圧縮にもつながります。

開発実績「規格関連」

| 分類 | 規格名 | バージョン | 開発実績あり |

| 映像関係 | HDMI | 1.4/2.0 | IC(TX,RX) FPGA_IP(TX,RX):Xilinx, Digilent |

| SDI | SD, HD, 3G, 12G | IC(TX,RX) FPGA_IP(TX,RX):Xilinx |

|

| DisplayPort | 1.0/1.2 | IC(RX) FPGA_IP(TX):自社オリジナル |

|

| MIPI CSI-2 | - | FPGA_IP(TX,RX):自社オリジナル,Xilinx, Lattice | |

| CoaXPress | - | IC(TX,RX) | |

| CameraLink | - | IC(TX,RX) FPGA_IP(TX,RX):自社オリジナル |

|

| CameraLink HS | - | FPGA_IP(TX,RX):自社オリジナル | |

| V-by-One® | - | IC(TX,RX) FPGA_IP(TX,RX):Xilinx, Intel |

|

| FPD-Link | - | IC(TX,RX) | |

| GVIF | - | IC(TX,RX) | |

| GMSL | - | IC(TX,RX) | |

| 高速シリアル | PCIe | - | IC(Endpoint) FPGA_IP(Root,Endpoint):Xilinx, Intel |

| USB | USB2.0/USB3.0(USB3.1 Gen1) | IC(Device) | |

| SATA | SATAⅠ/SATAⅡ/SATAⅢ | FPGA_IP:自社オリジナル | |

| 産業ネットワーク | CAN | - | マイコン FPGA_IP:自社オリジナル |

| Modbus | ASCII/RTU | マイコン | |

| EtherCAT | - | モジュール | |

| DeviceNet | - | IC |

開発実績「基板/FPGA/ソフト/複合案件」

※リスト上にカーソルを合わせてクリックしていただくと詳細説明にジャンプします

基板画像処理LSI評価基板の設計、製造

基板SoC-FPGA評価基板の設計、製造

FPGAASICでの顧客資産(RTL)をCベースsim用のモデルへ変換

FPGAEFINIX-FPGA評価ボードを使用したデモ機開発

ソフトLTEモジュールを使用したセンサ基板

複合案件画像取得装置

複合案件カメラ画像転送基板

複合案件SoC-FPGAの回路/ソフト設計

複合案件顧客基板とTOFセンサのブリッジ回路及び制御ソフト開発

複合案件VESA規格の圧縮伸長処理 DSC(Display Stream Compression) ハードウェア化

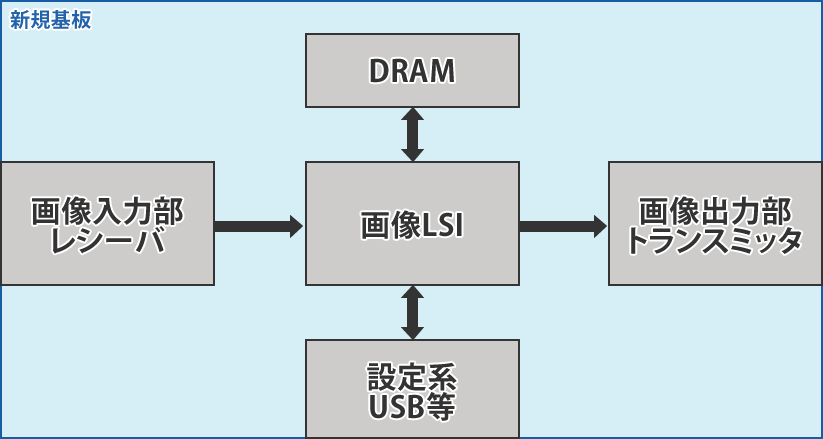

【基板】画像処理LSI評価基板の設計、製造

- 開発概要

- 画像処理LSIのI/Fに合わせて入出力部にレシーバ及びトランスミッタを配置し、各種信号・解像度への対応を可能とする

(HDMI、SDI、V-by-One®、LVDS、アナログRGB等)

画像処理LSIにはDRAM(主にDDR3)を配置し、設計系にはUSB2.0~SPI、I2C変換チップを採用する - 開発期間

- 回路設計 1ヶ月、アートワーク設計ほか 1ヶ月、基板製造 1ヶ月

※アートワーク/アートワークSIM、基板製造は協力会社に委託 - キーとなる技術

- 画像入出力(HDMI、アナログRGB、SDI、V-by-One®、LVDS)

DDR3 I/F SIシミュレーション

HDMI 4K30Hz - ブロック図

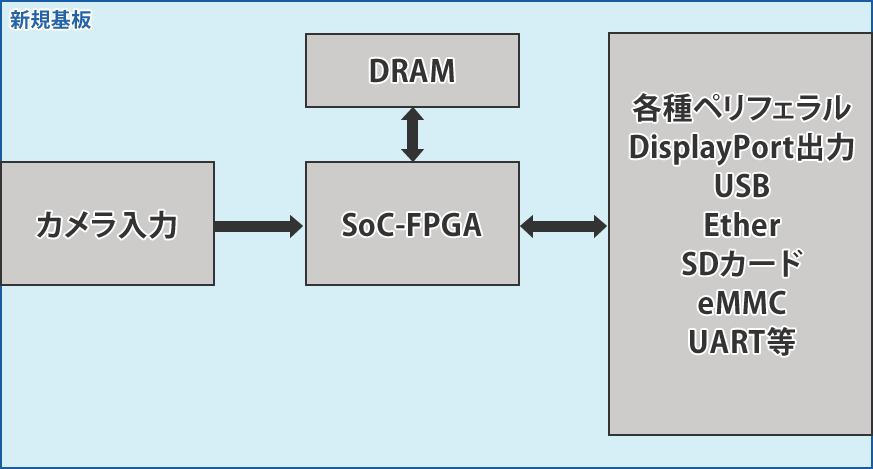

【基板】SoC-FPGA評価基板の設計、製造

- 開発概要

- Xilinx Zynq UltraScale+を使用した評価基板

Zynq UltraScale+に接続されるペリフェラルは、eMMC、SDC、SerialFlash、DisplayPort出力、USB2.0/3.0、イーサネット、UART、GPIO等

DRAM部はDDR4/LPDDR4

電源部はPIシミュレーションを実施 - 開発期間

- 回路設計 1.5ヶ月、アートワーク設計・シミュレーションほか 2ヶ月、基板製造 2ヶ月

※アートワーク/アートワークSIM、基板製造は協力会社に委託 - キーとなる技術

- 画像入出力(カメラ入力、Displayport出力)

DDR4 I/F、LPDDR4 SIシミュレーション

FPGA電源部PI解析(Power Integrity) - ブロック図

【FPGA】ASICでの顧客資産(RTL)をCベースsim用のモデルへ変換

- 開発概要

- RTLソースコードしかない状態で、コードからCモデルへの書き換えを実施

ランダム検証(カバレッジ95%以上)でRTLとCを比較検証 検証対象は30モジュール以上 - 開発期間

- 2.5ヶ月(FPGAエンジニア1名で対応)

- キーとなる技術

- コードカバレッジ検証

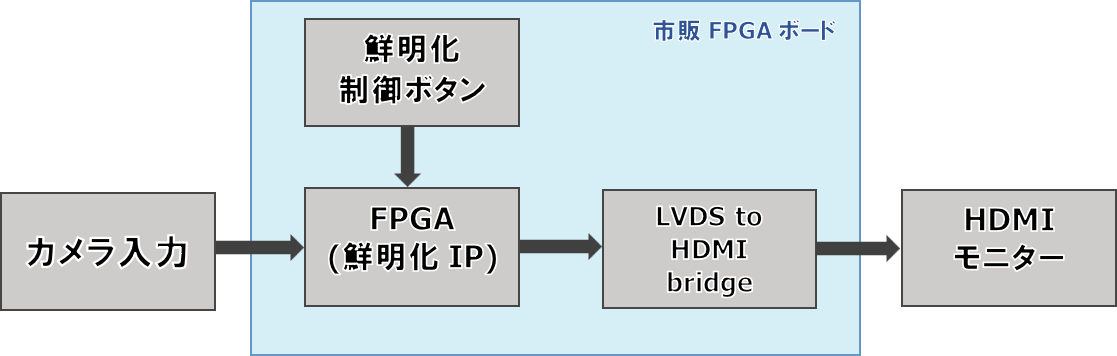

【FPGA】EFINIX-FPGA評価ボードを使用したデモ機開発

- 開発概要

- ラズパイカメラモジュールから映像を受け取り、リアルタイムで鮮明化処理を実行、処理結果をHDMI出力する回路を

市販FPGAボードに実装する

使用したボードは EFINIX社製「Trion T120BGA576 Development Kit」 - 開発期間

- 1.0ヶ月(FPGAエンジニア2名で対応)

- キーとなる技術

- MIPI CSI-2(カメラ入力)、LVDS(HDMI出力)、鮮明化処理、YUV<=>RGB色空間変換(ハード処理)

- ブロック図

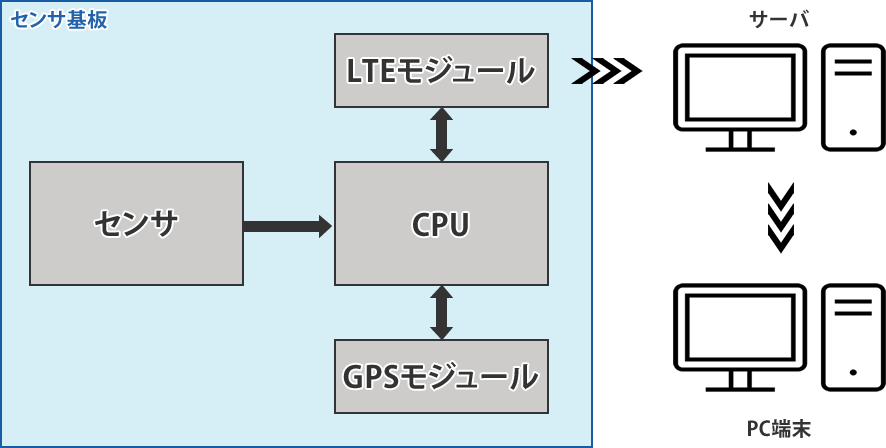

【ソフト】LTEモジュールを使用したセンサ基板

- 開発概要

- センサ取得値とGPS取得情報を、LTEモジュールを用いてサーバに書き込み、PC端末で管理する

マイコンのファームウェア設計を担当し、「センサ値取得」「GPSデータ取得」「LTEモジュール間アクセス」機能を組み込む - 開発期間

- ファームウェア設計 1.5ヶ月

- キーとなる技術

- LTEモジュール制御

GPSモジュール制御

センサデータ取得 - ブロック図

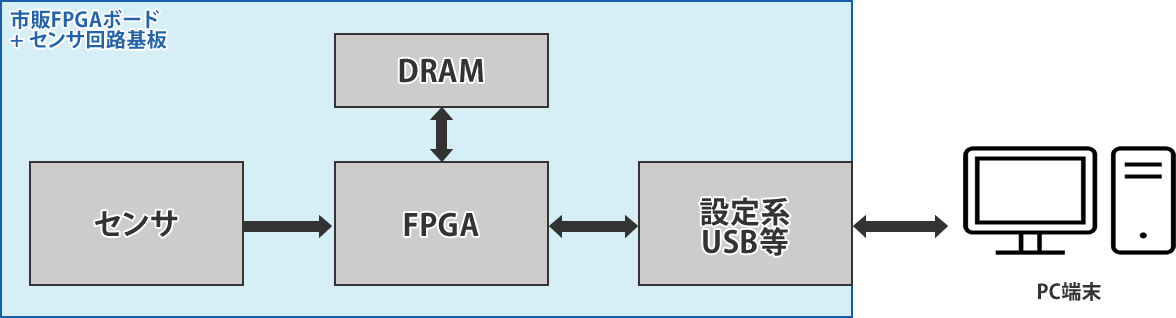

【複合案件】画像取得装置

- 開発概要

- 市販FPGAボードに、顧客の画像取り込みセンサ回路基板を接続したハード構成

センサからの画像データをFPGAで受け、メカ(エンコーダ)からのパルスに同期して光源制御・画像取得を行い、DRAMに格納する

取得した画像に対してシェーディング、平均化等の処理を行い、USBを介して、PCにデータを送信する

PC側アプリケーションには「取得したデータのグラフ化」「二次元化」「データ保存」機能を実装する - 開発期間

- FPGA設計 1ヶ月、PCアプリ設計 1ヶ月、評価 1.5ヶ月

- キーとなる技術

- センサ画像取得(FPGA)

センサ光源制御(FPGA)

メカと同期して画像を取得(FPGA)

取得画像処理技術(PCアプリ) - ブロック図

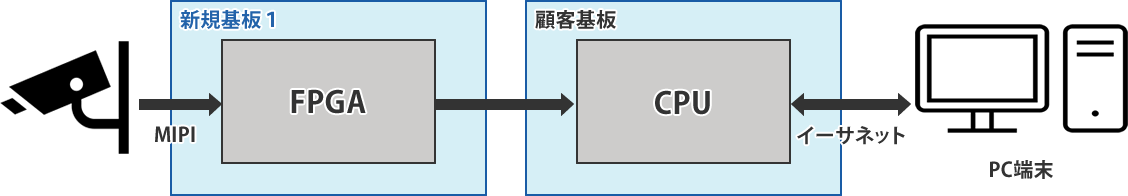

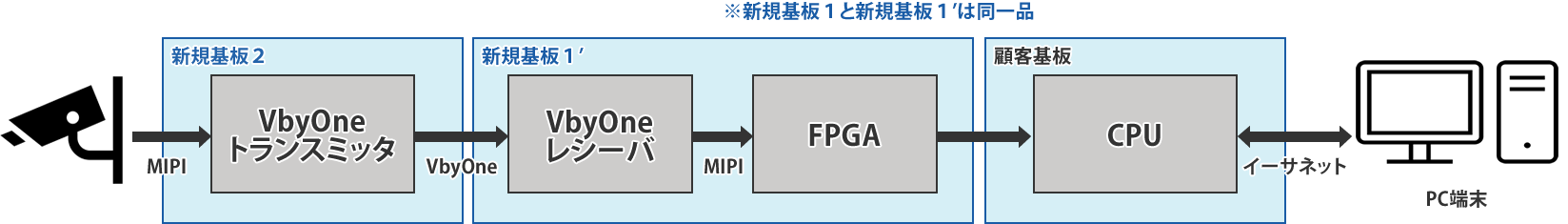

【複合案件】カメラ画像転送基板

- 開発概要

- 産業用カメラ(MIPI出力)の信号を受け、顧客のCPUボード(パラレルバス受け)向けにデータ変換して信号を渡すハード構成

ブロック図2のように、間にV-by-One®を挟むことで、カメラとCPU基板の配置が離れた場合にも対応できるようにする - 開発期間

- 基板設計(回路、アートワーク) 1ヶ月、FPGA設計 0.5ヶ月、評価 1.5ヶ月、基板製造 1ヶ月

※基板製造は協力会社に委託 - キーとなる技術

- MIPI画像入力

MIPI-Parallel変換(FPGA)

V-by-One®画像入出力 - ブロック図1

- ブロック図2

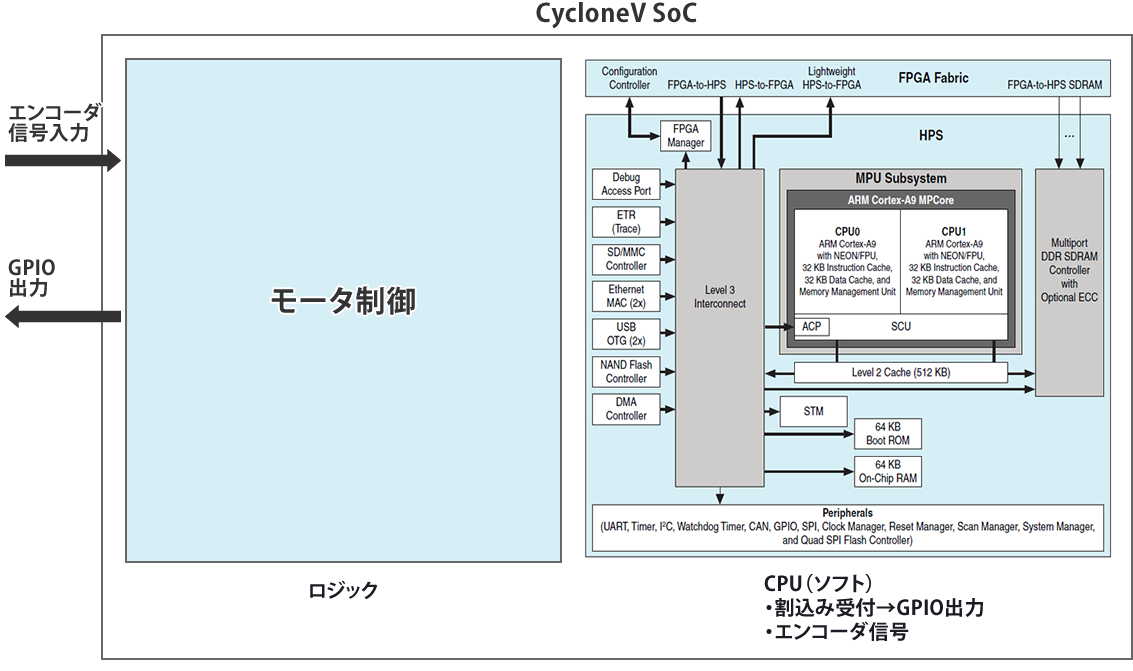

【複合案件】SoC-FPGAの回路/ソフト設計

- 開発概要

- モータ制御用に使用する基板上のCycloneVSoCに、モータIFと動作制御用のARMソフトを実装する

- 開発期間

- 1.5ヶ月(FPGAエンジニア1名で対応)

- キーとなる技術

- SoC-FPGAのロジック/ARM複合制御

- FPGAブロック図

- FPGA開発環境

-

FPGA開発環境 備考 開発環境 Quartus15.1 ベース環境 cv_soc_devkit_ghrd Intel CycloneV SoC Development kit

Golden Hardware Reference Design (GHRD)言語 Verilog 確認用のエンコーダのエミュレート機能のみ設計、その他は

QSYS-IP を使用バス Avalon FPGA内部は Avalon で接続 MPUクロック 925MHz スピードグレードC6 の最高速度 ベース環境のまま MPU SDRAM 400MHz ECC ベース環境のままでECC付きで作成 FPGA 内部ローカル

バスクロック50MHz ベース環境のままで50MHz HPS2FPGA接続 HPS2FPGALW LowWeightポートを使用して、HPS(Master)からFPGAに

アクセスする - HPS開発環境

-

HPS開発環境 備考 開発環境 SoCEDS 15.1.1 ツールチェーン GNU-GCC 今回はGNU-GCCを使用(ARMCCで作成することも可能) 言語 C言語 使用ライブラリ Intel HWLib

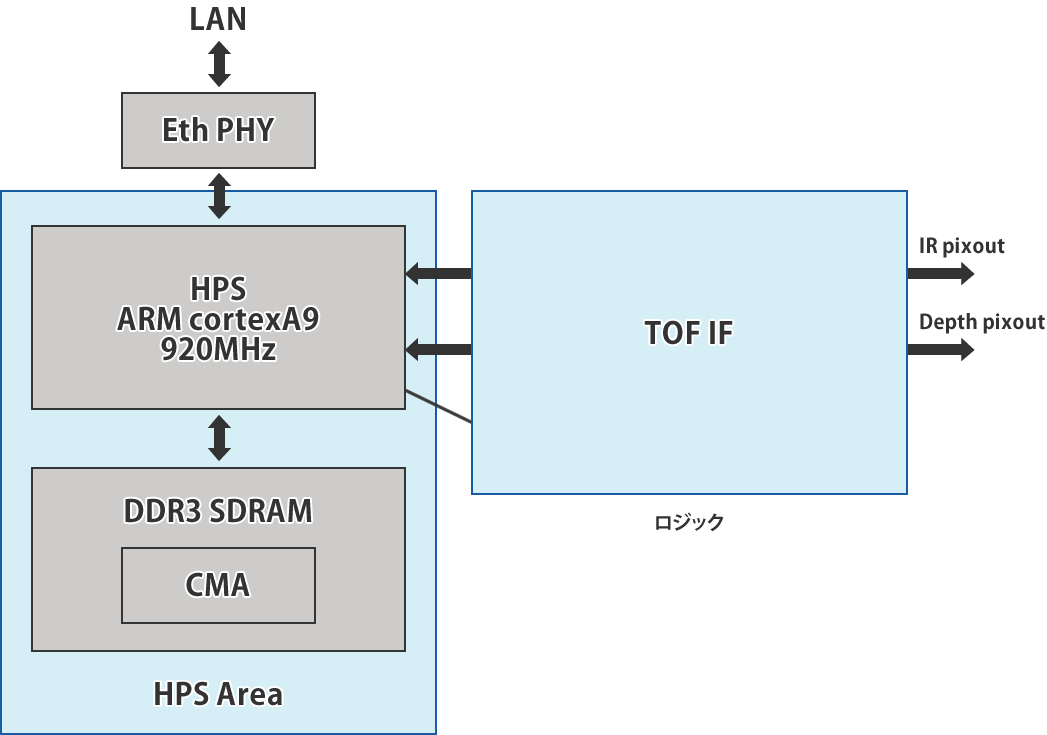

【複合案件】顧客基板とTOFセンサのブリッジ回路及び制御ソフト開発

- 開発概要

- 顧客基板からTOFカメラへの各種設定及びデータ受信を行うFPGA回路設計とソフト設計を行う

ブリッジには自社製FPGAボード"ZSOC002"を採用し、開発期間短縮とコストダウンを実現している - 開発期間

- 2ヶ月(FPGAエンジニア1名で対応)

- キーとなる技術

- TOFセンサ制御(ドライバソフトの変更も含む)

- FPGAブロック図

- 基板概要

【複合案件】VESA規格の圧縮伸長処理 DSC(Display Stream Compression) ハードウェア化

- 開発概要

- FPGAへ搭載、4kディスプレイ用

CアルゴリズムをRTLへ変換、高位合成では規模/性能が出ないことが判明したため高速化/小規模化設計を実施

→最終的に、市販IPと同等性能で回路規模40%弱小さい回路を構築できた

並行して基板設計を実施

→DisplayPort IF 5.4Gbpsの速度でのディスプレイ接続を実現できた - 開発期間

- 2ヶ月強(FPGAエンジニア1名、基板エンジニア1名で対応)

※基板製造は協力会社に委託 - キーとなる技術

- VESA DSC制御

※「V-by-One®」はザインエレクトロニクス株式会社の登録商標です

English

English オプテックス株式会社の詳細はこちら

オプテックス株式会社の詳細はこちら