# ZEN7251G データシート

株式会社ジーニック

# Left blank

# 目次

| 1. 概要                         | 1 |

|-------------------------------|---|

| 2. 特徴                         | 1 |

| 3. システムブロック構成                 | 2 |

| 4. 端子一覧                       | 3 |

| 4.1. PCIバス・インタフェース信号          | 3 |

| 4.2. EEPROMコントロール信号           | 4 |

| 4.3. ローカルバス・インタフェース信号         | 4 |

| 4.4. デバッグ信号                   | 6 |

| 4.5. 電源・グランド及びテスト信号           | 6 |

| 5. 基本仕様                       | 7 |

| 5.1. 対応PCIバス                  |   |

| 5.2. 電源電圧                     | 7 |

| 5.3. 信号電圧                     | 7 |

| 5.4. ローカルデータバス                | 7 |

| 5.5. ローカルアドレスバス               | 7 |

| 5.6. ローカルクロック                 | 7 |

| 5.7. EEPROM                   | 7 |

| 6. PCIバスアクセス                  | 9 |

| 6.1. 対応PCIコマンド                | 9 |

| 6.1.1.ターゲットアクセス<br>6.1.2. DMA |   |

|                               |   |

| 6.2. ディレイド・リード                 | 11 |

|--------------------------------|----|

| 6.3. ポスティッド・ライト                | 11 |

| 6.4. 例外処理                      | 12 |

| 6.4.1.ターゲットアクセス<br>6.4.2. DMA  |    |

| 6.5. ディスコネクト                   | 13 |

| 6.5.1.ターゲットアクセス<br>6.5.2. DMA  |    |

| 6.6. リトライ                      | 13 |

| 6.6.1. ターゲットアクセス<br>6.6.2. DMA |    |

| 7. ローカルアクセス                    | 14 |

| 7.1. 概要                        | 14 |

| 7.2. ローカルI/Oアクセス               | 15 |

| 7.3. ローカルメモリアクセス               | 15 |

| 7.4. アドレッシング (バンクレジスタ)         | 16 |

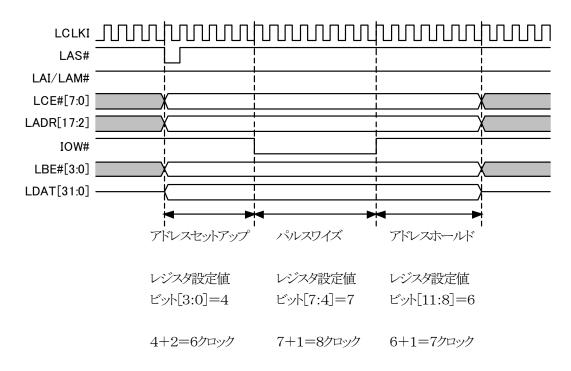

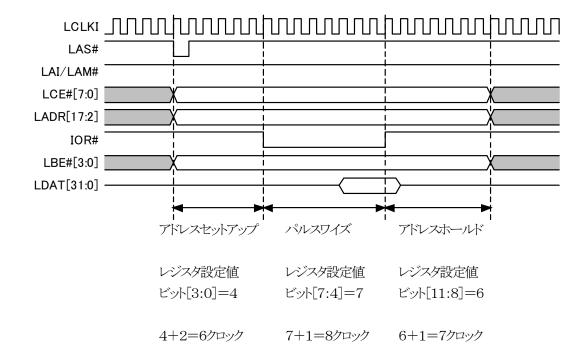

| 7.5. タイミングコントロール               | 16 |

| 7.6. リードプリフェッチ(メモリアクセス)        |    |

| 8. DMA                         | 17 |

| 8.1. 概要                        | 17 |

| 8.2. 転送回数                      | 17 |

| 8.3. 転送領域                      | 17 |

| 8.4. 転送方向                      | 17 |

| 8.5. バースト長(PCIバス)              | 17 |

| 8.6. アドレッシング                        | 18 |

|-------------------------------------|----|

| 8.7. 起動/終了                          | 18 |

| 8.7.1. 通常起動/通常終了                    | 18 |

| 8.7.2. 強制終了                         |    |

| 8.7.3. ターゲットアボート                    |    |

| 8.7.4. マスタアボート                      | 18 |

| 8.8. リレー転送                          | 19 |

| 9. その他の機能                           | 20 |

| 9.1. 汎用I/Oポート                       | 20 |

| 9.2. PCIクロックタイマ                     | 20 |

| 9.3. 割り込み                           | 20 |

| 9.3.1. IRQ#                         | 20 |

| 9.3.2. PCIクロックタイマ                   |    |

| 9.3.3. DMA転送終了                      |    |

| 9.4. デバッグ用アドレスマッチ信号                 | 21 |

| 10. レジスタ                            | 22 |

| 10.1. PCIコンフィギュレーションレジスタ            | 22 |

| 10.1.1.レジスタマップ                      | 22 |

| 10.1.2. レジスター覧                      | 00 |

| 10.2. モードレジスタ                       | 28 |

| 10.2.1. レジスタマップ                     | 28 |

| 10.2.2. レジスター覧                      | 29 |

| 11. タイミングチャート                       | 41 |

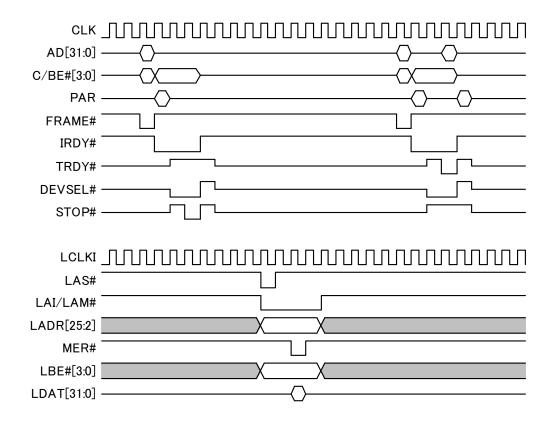

| 11.1.ターゲットアクセス                      | 41 |

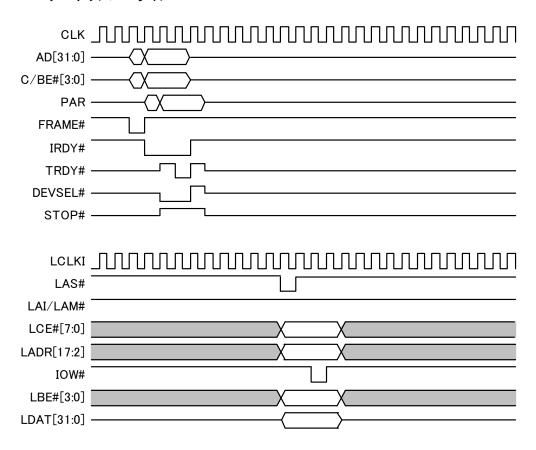

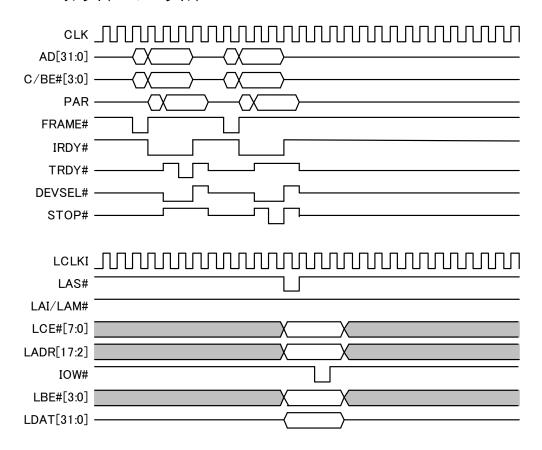

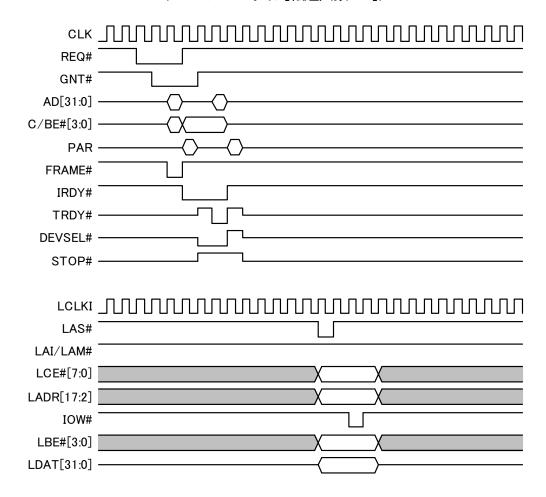

| 11.1.1.ターゲットI/Oライト                  | 41 |

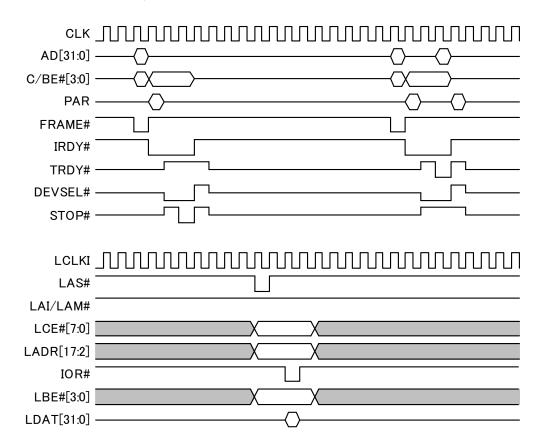

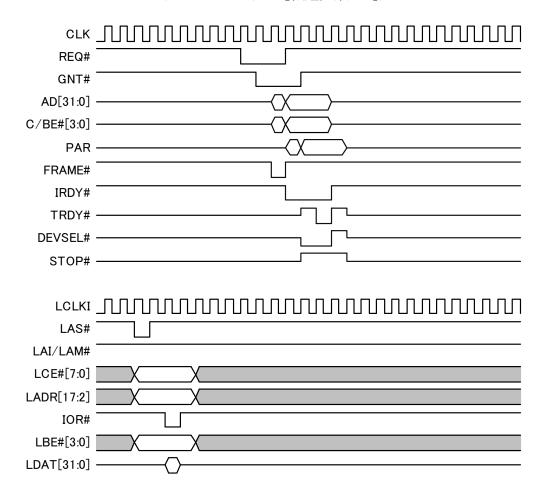

| 11.1.2. ターゲットL/Oリード                 |    |

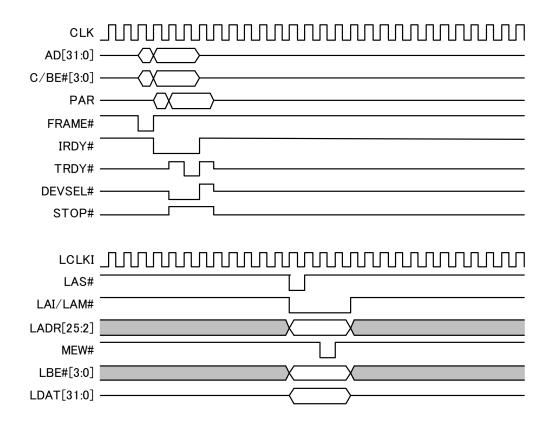

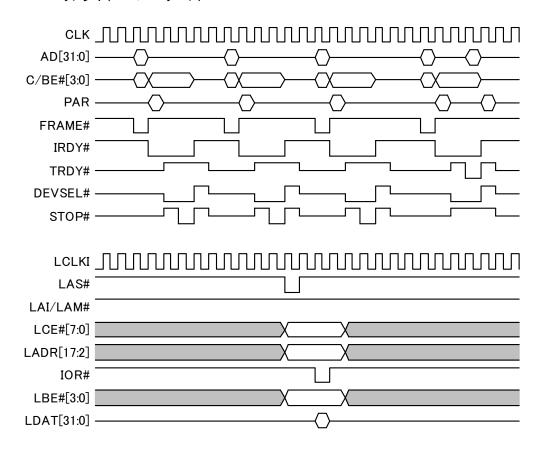

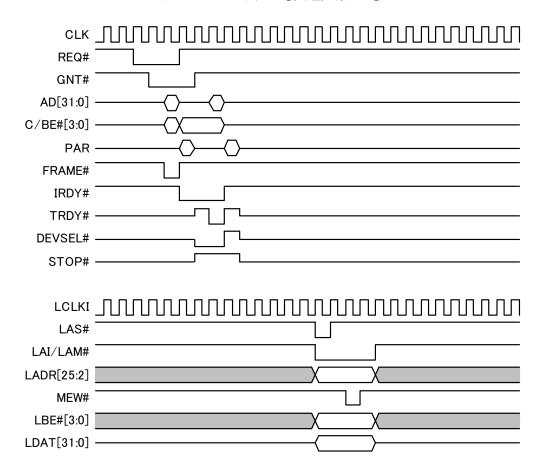

| 11.1.3. ターゲットメモリライト                 |    |

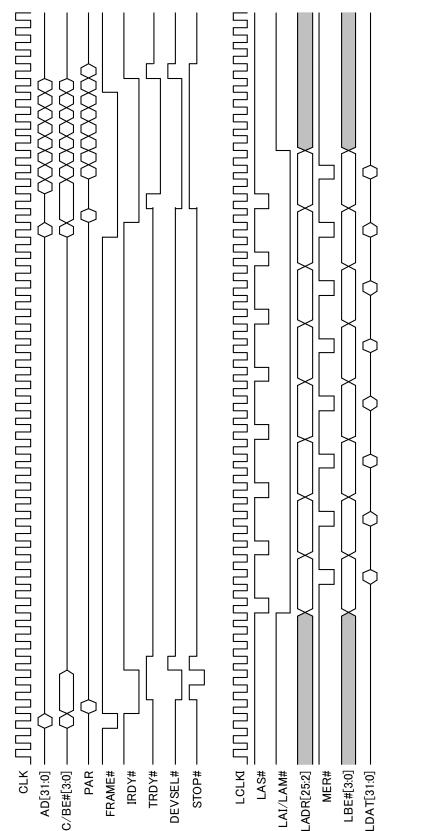

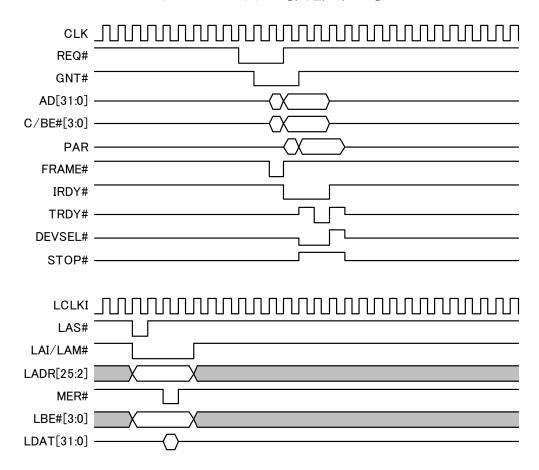

| 11.1.4. ターゲットメモリリード(プリフェッチなし)       | 44 |

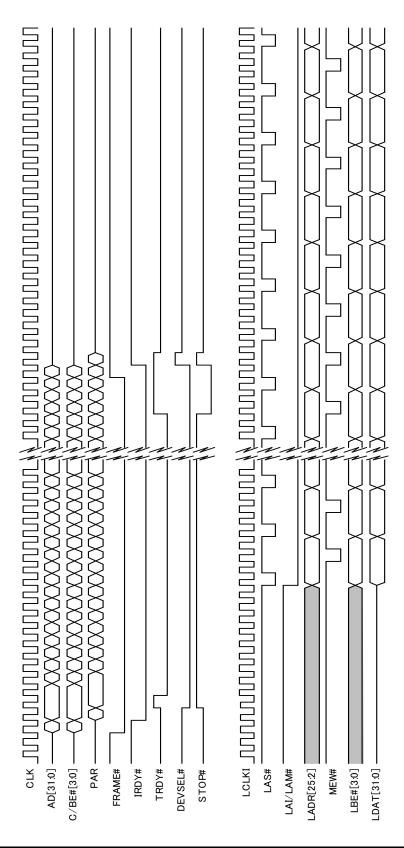

| 11.1.5. ターゲットメモリリード(プリフェッチ8データ)     |    |

| 11.1.6.レジスタ設定によるタイミングコントロール(I/Oライト) | 46 |

|                                                    | 46   |

|----------------------------------------------------|------|

| 11.1.8.レジスタ設定によるタイミングコントロール(メモリライト)                | 47   |

| 11.1.9.レジスタ設定によるタイミングコントロール(メモリリード)                |      |

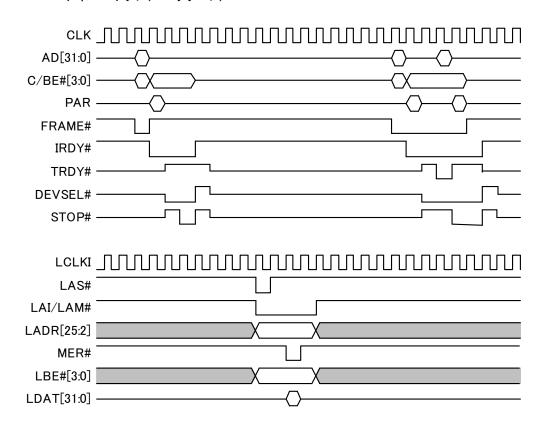

| 11.1.10.WAIT#によるタイミングコントロール(ex. I/Oライト)            | 48   |

| 11.1.11.WAIT#によるタイミングコントロール詳細(ex. I∕Oライト)          | 49   |

| 11.1.12.リトライ(ex. I/Oライト)                           |      |

| 11.1.13. リトライ(ex. I/Oリード)                          |      |

| 11.1.14. ディスコネクト(メモリライト)                           |      |

| 11.1.15. ディスコネクト(メモリリード)                           | 53   |

| 11.2. DMA                                          | 54   |

| 11.2.1.PCI to ローカル(ローカルI/Oライト[転送回数=1])             | 54   |

| 11.2.2.ローカル to PCI(ローカルI/Oリード[転送回数=1])             | 55   |

| 11.2.3.PCI to ローカル(ローカルメモリライト[転送回数=1])             |      |

| 11.2.4.ローカル to PCI(ローカルメモリリード[転送回数=1])             | 57   |

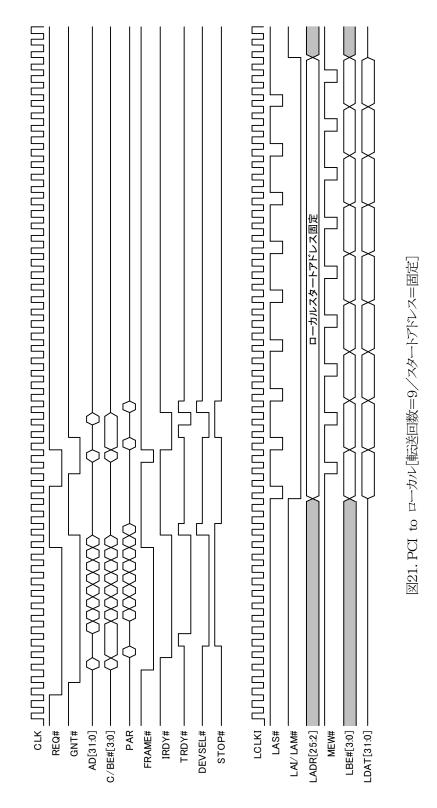

| 11.2.5.PCI to ローカル(ローカルメモリライト[転送回数=9/スタートアドレス=固定]  | ])58 |

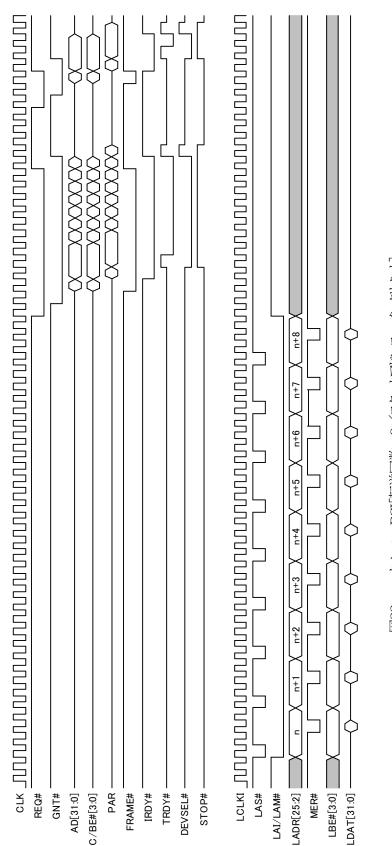

| 11.2.6. ローカル to PCIバースト(ローカルメモリリード[転送回数=9/スタートアドレス |      |

| h]                                                 | 59   |

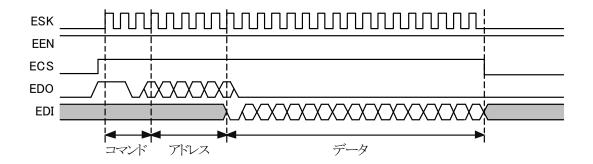

| 11.3. EEPROMによる初期化                                 | 60   |

| 12. 電気的特性                                          | 61   |

|                                                    | 0.1  |

| 12.1. 絶対最大定格                                       | 01   |

| 12.2. 推奨動作条件                                       | 61   |

| 12.2.                                              | 01   |

| 12.3. 直流特性                                         | 61   |

|                                                    |      |

| 12.4. 交流特性                                         | 62   |

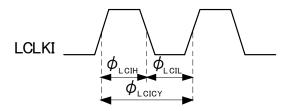

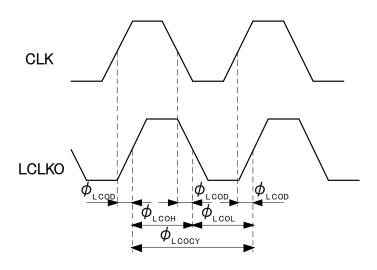

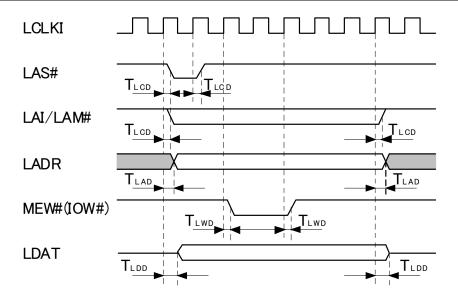

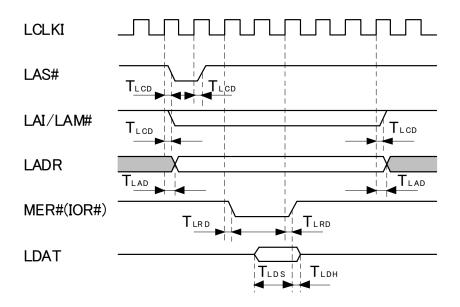

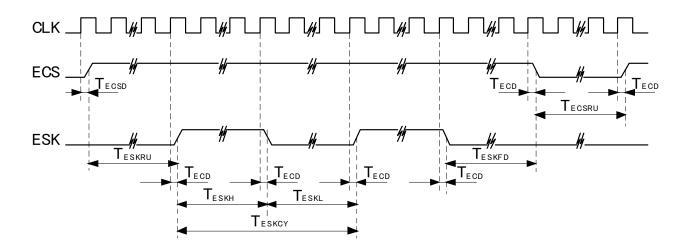

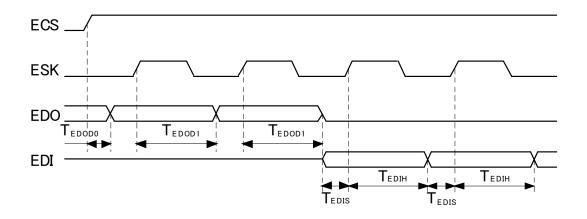

| 12.5. タイミングダイアグラム                                  | 63   |

|                                                    |      |

| 12.5.1. ローカルアクセスタイミングダイアグラム                        |      |

| 12.5.2. EEPROMアクセスタイミングダイアグラム                      |      |

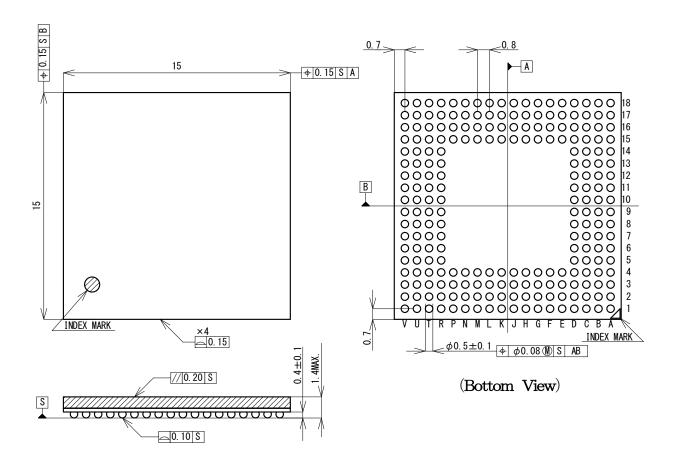

| 13. パッケージ形状                                        | 66   |

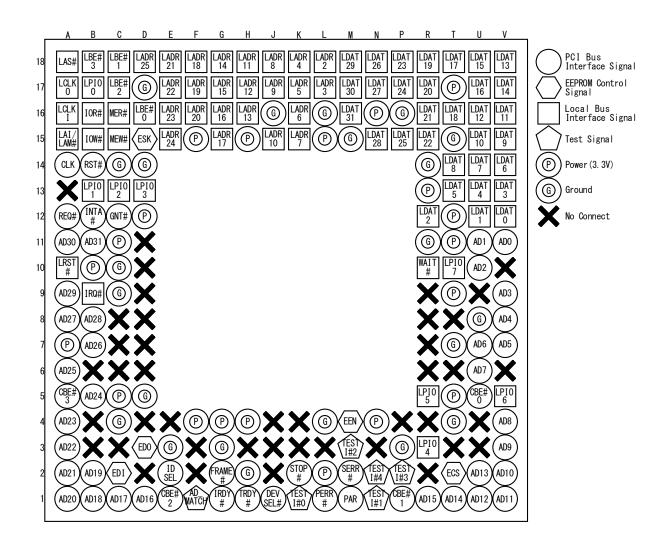

| 14. 端子配置                                           | 67   |

|                                                    |      |

| 15. 改訂履歴                                           | 68   |

# Left blank

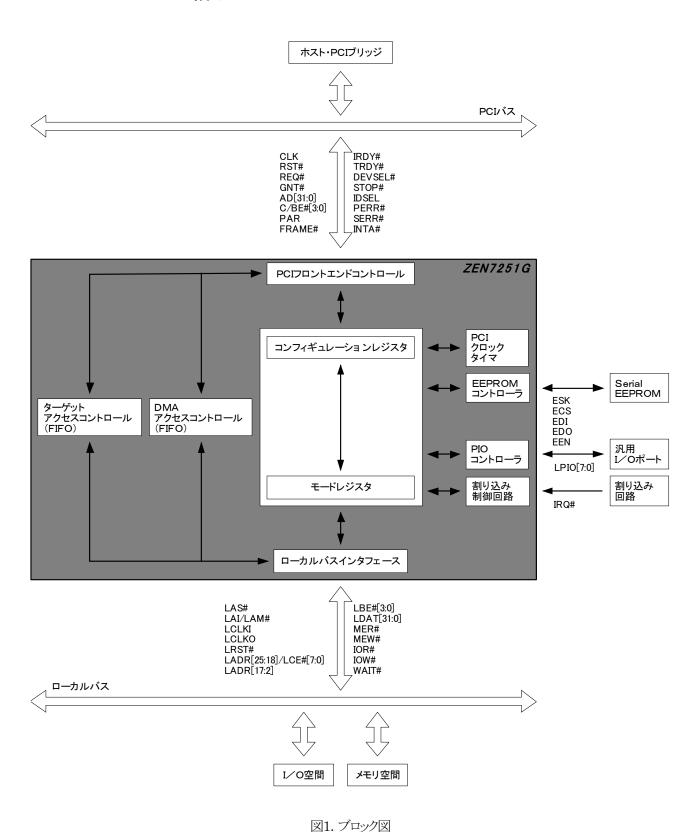

### 1. 概要

**ZEN7251G** はPCI(Revision2. 2)及びCompactPCI(Revision1. 0)に準拠したターゲットアクセス&DMA内蔵PCIバス・インタフェースICです。32bit・33MHzのPCIバス(5V)に対応します。ローカル側に最大64Mbyteのメモリ空間と64KbyteのI/O空間を持つことができます。ローカルのデータバスは32bit、アドレスバスは26bitです。ローカルアドレスは内蔵のバンクレジスタを使用することにより、コンフィギュレーションレジスタで割り当てられたサイズ以上の空間を使用することができます。

メモリ領域へのターゲットアクセス及びDMA転送を処理するデータパスには32段の大容量FIFOを内蔵しており、効率的なPCI―→ローカル間のデータ転送をサポートします。また、大容量データを効率よく転送するために、DMA設定レジスタ群を4組内蔵しています。本レジスタを活用することにより、ホスト側のメモリを連続して確保できない場合でも、バス効率を落とさずに4つの分散したメモリ領域へ一度にDMA転送が可能です。ローカルバスの信号タイミングはレジスタ設定により調整可能です。また、WAIT#端子により動的にタイミングをコントロールすることもできます。ローカルバスのクロック周波数は最大50MHzです。パッケージには超小型のLFBGA224を採用し、ショートカードサイズの基板でもスペースを有効に活用できます。

# 2. 特徴

- ○32bit・33MHzのPCIバス(5V)に対応

- ○電源電圧3.3V単一

- ○入力(入出力)端子は5Vトレラント(PCI/ローカル)

- ○ローカルクロック入力周波数は最大50MHz

- ○ローカルメモリ空間最大64Mbyte、ローカルI/O空間最大64Kbyte

- ○ローカルバスはインタフェース設計が容易なストローブ方式

- ○汎用PCIクロックタイマ内蔵(32bit)

- ○ローカルデータバス幅32bit

- ○DMA・PCIスタートアドレス、DMA・ローカルバススタートアドレス及び転送回数設定レジスタを4組装備

- ○I/Oアクセス用アドレスデコーダを内蔵

- ○モードレジスタ及びWAIT#信号によってローカルアクセスタイミングを調整可能

- ○ターゲットアクセス(メモリ)・DMA転送それぞれ独立に32段のFIFOを装備

- 〇ローカル側の割り込み信号(IRQ#)をPCIのINTA#として出力

- ○CompactPCI対応(ホットスワップ非対応)

- ○224ピンBGAパッケージ(ボールピッチ0.8mm)

# 3. システムブロック構成

**21.** 7 · 77 E

# 4. 端子一覧

# 4.1. PCIバス・インタフェース信号

表1. PCIバス・インタフェース信号(その1)

| 端子番号                                                                                                                                                        | 記号             | 信号名                          | 属性  | 機能                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|-----|-------------------------------------------------------------------------------------------------------|

| A14                                                                                                                                                         | CLK            | PCI Clock                    | IN  | PCレバス上にあるすべてのデバイスの動作基準となる<br>クロックです。INTA#、RST#以外のPCレバス・インタ<br>フェース信号はすべてこのクロックに同期して動作し<br>ます。         |

| B14                                                                                                                                                         | RST#           | PCI Reset                    | IN  | PCIバス上のデバイスをリセットします。                                                                                  |

| A12                                                                                                                                                         | REQ#           | Bus Request                  | OUT | PCIバスの使用権をバス・アービタに対して要求します。                                                                           |

| C12                                                                                                                                                         | GNT#           | Bus Grant                    | IN  | バス・アービタからのPCIバス使用許可信号です。                                                                              |

| B11, A11, A9,<br>B8, A8, B7, A6,<br>B5, A4, A3, A2,<br>A1, B2, B1, C1,<br>D1, R1, T1, U2,<br>U1, V1, V2, V3,<br>V4, U6, U7,<br>V7, V8, V9,<br>U10, U11, V11 | AD[31:0]       | Address/Data                 | I/O | アドレス・データバスは時分割に32本の信号線をドライブします。バスサイクルは1回のアドレスフェーズとそれに続くデータフェーズからなり、アドレスフェーズでアドレスが、データフェーズでデータが出力されます。 |

| A5, E1, P1, U5                                                                                                                                              | C/BE#<br>[3:0] | Bus Command /Byte Enable     | I/O | バスコマンド・バイトイネーブルはAD[31:0]と同様時<br>分割にこの4本の信号をドライブします。アドレス<br>フェーズでバスコマンドが、データフェーズではバイト<br>イネーブルが出力されます。 |

| M1                                                                                                                                                          | PAR            | Parity                       | I/O | AD、C/BE#の36本に偶数パリティを付加します。<br>36本のうち、値が"1"のビットの合計が偶数のとき"0"<br>を、奇数のとき"1"を出力します。                       |

| G2                                                                                                                                                          | FRAME#         | Cycle Frame                  | I/O | サイクルの開始を知らせる信号です。この信号はアドレスフェーズの開始と同時にアサートされます。この信号がアサートされるとサイクルが始まり、ディアサートされると次のデータフェーズでサイクルが終了します。   |

| G1                                                                                                                                                          | IRDY#          | Initiator Ready              | I/O | マスタがデータ転送可能であるときにアサートされます。                                                                            |

| H1                                                                                                                                                          | TRDY#          | Target Ready                 | I/O | ターゲットがデータ転送可能であるときにアサートされます。                                                                          |

| J1                                                                                                                                                          | DEVSEL#        | Device Select                | I/O | マスタからのアクセスに応答するかどうかを示す信号です。アクセスを受け入れたターゲットがサイクル終了までアサートします。                                           |

| K2                                                                                                                                                          | STOP#          | Bus Stop                     | I/O | サイクルを実行中のターゲットがマスタに向けてサイクルの中断を要求するときにアサートします。                                                         |

| E2                                                                                                                                                          | IDSEL          | Initialization Device Select | IN  | コンフィギュレーションサイクルの対象となるデバイスを<br>選択するのに使用します。                                                            |

# 表2. PCレベス・インタフェース信号(その2)

| 端子番号 | 記号    | 信号名          | 属性  | 機能                                                                                                                                                        |

|------|-------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| L1   | PERR# | Parity Error | I/O | スペシャルサイクルを除くサイクルにおいて、デバイス<br>がアドレスパリティーエラー、データパリティーエラーを<br>検知したときにこの信号をアサートします。ライトサイク<br>ルではターゲットが、リードサイクルではマスタがこの<br>信号をドライブします。また、この信号の処理はマスタ<br>が行います。 |

| M2   | SERR# | System Error | OUT | システムにとって致命的なエラーを検知したデバイスがこの信号をアサートします。                                                                                                                    |

| B12  | INTA# | Interrupt    | OUT | 割り込み発生時にアサートされます。                                                                                                                                         |

# 4.2. EEPROMコントロール信号

#### 表3. EEPROMコントロール信号

| 端子番号              | 記号   | 信号名         | 属性  | 機能                         |

|-------------------|------|-------------|-----|----------------------------|

| D15               | ESK  | EEPROM      | OUT | EEPROMのクロック信号です。この信号はEEPRO |

| D10               | ESIX | Clock       | 001 | MのSKと接続します。                |

| T2                | ECS  | EEPROM      | OUT | EEPROMのチップセレクト信号です。この信号はEE |

| 12                | ECS  | Chip Select | 001 | PROMのCSと接続します。             |

| C2                | EDI  | EEPROM      | IN  | EEPROMからのデータを入力します。この信号はEE |

| C2                | EDI  | Data IN     | пл  | PROMのDOと接続します。             |

| D3                | EDO  | EEPROM      | OUT | EEPROMへのデータを出力します。この信号はEEP |

| Do                | EDO  | Data OUT    | 001 | ROMのDIと接続します。              |

| M4                | EEN  | EEPROM      | IN  | この信号が"1"のとき、リセット解除後初期化のために |

| 1V1 <del>'1</del> | THEN | Enable      | πи  | EEPROMからデータを読み出します。        |

# 4.3. ローカルバス・インタフェース信号

#### 表4. ローカルバス・インタフェース信号(その1)

| 端子番号 | 記号           | 信号名                       | 属性  | 機能                                                                               |

|------|--------------|---------------------------|-----|----------------------------------------------------------------------------------|

| A18  | LAS#         | Local Access<br>Start     | OUT | ローカルアクセスのスタートを示し、サイクルの最初の<br>1クロックのみ"0"を出力します。                                   |

| A15  | LAI/<br>LAM# | Local Access I/O/Memory   | OUT | ローカルデバイスへのアクセスを識別する信号です。<br>この信号が"0"のときメモリアクセスが、"1"のときI/O<br>アクセスが発生しています。       |

| A16  | LCLKI        | Local<br>Clock Input      | IN  | ローカルデバイスをコントロールするためのクロック入力です。 <b>ZEN7251G</b> が出力するローカルクロック(LC LKO)を接続することも可能です。 |

| A17  | LCLKO        | Local Clock<br>33M Output | OUT | ローカルデバイスをコントロールするためのクロック出力です。この信号はPCIクロックをそのまま(33MHz)<br>出力します。                  |

| A10  | LRST#        | Local Reset               | OUT | ローカルデバイスをリセットするための信号です。                                                          |

表5. ローカルバス・インタフェース信号(その2)

| 端子番号                                                                                                                                                                                     | 記号                                    | 信号名                              | 属性  | 機能                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------|-----|---------------------------------------------------------------|

| M16, M17,<br>M18, N15,<br>N17, N18, P15,<br>P17, P18, R15,<br>R16, R17, R18,<br>T16, T18, U17,<br>U18, V17, V18,<br>U16, V16, U15,<br>V15, T14, U14,<br>V14, T13, U13,<br>V13, R12, U12, | LDAT<br>[31:0]                        | Local Data                       | I/O | ローカルデバイスとの間でデータ転送を行うための信号です。                                  |

| D18, E15, E16,<br>E17, E18, F16,<br>F17, F18                                                                                                                                             | LADR<br>[25:18]<br>/<br>LCE#<br>[7:0] | Local Address  Local Chip Enable | OUT | ローカルデバイスへのアクセスを行うためのアドレス信号です。I/Oアクセス時にはI/O空間のチップイネーブル信号となります。 |

| G15, G16, G17,<br>G18, H16, H17,<br>H18, J15, J17,<br>J18, K15, K16,<br>K17, K18, L17,<br>L18                                                                                            | LADR<br>[17:2]                        | Local Address                    | OUT | ローカルデバイスへのアクセスを行うためのアドレス信号です。                                 |

| B18, C17, C18,<br>D16                                                                                                                                                                    | LBE#[3:0]                             | Local Byte<br>Lane Enable        | OUT | ローカルバスの有効なバイトレーンを示します。                                        |

| C16                                                                                                                                                                                      | MER#                                  | Memory Read                      | OUT | ローカルデバイスへのメモリリードアクセスを行うときに<br>アサートされます。                       |

| C15                                                                                                                                                                                      | MEW#                                  | Memory Write                     | OUT | ローカルデバイスへのメモリライトアクセスを行うときに<br>アサートされます。                       |

| B16                                                                                                                                                                                      | IOR#                                  | I/O Read                         | OUT | ローカルデバイスへのI/Oリードアクセスを行うときに<br>アサートされます。                       |

| B15                                                                                                                                                                                      | IOW#                                  | I/O Read                         | OUT | ローカルデバイスへのI/Oライトアクセスを行うときに<br>アサートされます。                       |

| R10                                                                                                                                                                                      | WAIT#                                 | Access Wait                      | IN  | この信号を"0"にすることによって、ストローブ信号が<br>ディアサートするタイミングを遅らせることができます。      |

| В9                                                                                                                                                                                       | IRQ#                                  | Interrupt<br>Request             | IN  | ローカル側で発生した割り込み要求をPCIバスに知らせるための信号です。                           |

| T10, V5, R5,<br>R3, D13, C13,<br>B13, B17                                                                                                                                                | LPIO[7:0]                             | Local I/O<br>Port                | I/O | 8bitのプログラマブルI/Oポートです。                                         |

# 4.4. デバッグ信号

## 表6. デバッグ信号

| 端子番号 | 記号    | 信号名     | 属性  | 機能                            |

|------|-------|---------|-----|-------------------------------|

| F1   | AD_   | Address | OUT | PCIからのアクセスが ZEN7251G のいずれかのべー |

|      | MATCH | Match   | OUT | スアドレスとマッチするとアサートされます。         |

# 4.5. 電源・グランド及びテスト信号

#### 表7. 電源・グランド及びテスト信号

| 端子番号                                                                                                                                                                                                        | 記号              | 信号名           | 属性 | 機能                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----|---------------------------------------|

| N2, P2, M3,<br>N1, K1                                                                                                                                                                                       | TESTI#<br>[4:0] | Test<br>Input | IN | テスト用の入力端子です。通常使用時は必ずVDD<br>につないでください。 |

| A7, B10, C5,<br>C11, D12, F4,<br>F15, G4, H4,<br>H15, L2, L15,<br>N4, N16, R13,<br>T5, T9, T11,<br>T12, T17                                                                                                 | VDD             | VDD           | _  | 電源端子です(+3.3V)。                        |

| C4, C9, C10,<br>C14, D5, D14,<br>D17, E3, G3,<br>H2, J16, L4,<br>L16, M15, P3,<br>P16, R11, R14,<br>T4, T7, T15,<br>U8                                                                                      | GND             | Ground        | _  | グランド端子です。                             |

| A13, B3, B4,<br>B6, C3, C6, C7,<br>C8, D2, D4, D6,<br>D7, D8, D9,<br>D10, D11, E4,<br>F2, F3, H3, J2,<br>J3, J4, K3, K4,<br>L3, N3, P4, R2,<br>R4, R6, R7, R8,<br>R9, T3, T6, T8,<br>U3, U4, U9,<br>V6, V10 | N. C.           | No Connection | _  | 空き端子です。どこにも接続せず空けておいてください。            |

## 5. 基本仕様

#### 5.1. 対応PCIバス

ZEN7251G は周波数33MHz/バス幅32bit/信号電圧5VのPCI規格Revision2. 2に準拠したPCIバスに対応しています。 ZEN7251G の動作電源電圧は3. 3Vですが3. 3V規格のPCIバスには対応していませんのでご注意ください。

#### 5.2. 電源電圧

ZEN7251G は3. 3V単一電源で動作します。

#### 5.3. 信号電圧

ZEN7251GはPCI側及びローカル側すべての入力(入出力)端子が5Vトレラントになっています。

#### 5.4. ローカルデータバス

ZEN7251Gのローカル側のデータバス幅は32bit固定です。

### 5.5. ローカルアドレスバス

**ZEN7251G** のローカル側のアドレス端子は24本です。なお、アドレッシングはLongWord(32bit)単位になりますのでLAD R[25:2]と表記しています。

#### 5.6. ローカルクロック

**ZEN7251G** のローカルクロックは最大50MHzまで入力可能です。なお、33MHzのPCIクロックをローカル側に出力していますので、それを **ZEN7251G** のローカルクロックとして使うこともできます(LCLKOとLCLKIを外部で結線してください)。

#### 5.7. EEPROM

ZEN7251G は外付けの1Kbit MICROWIRE Serial Access EEPROM (STMicroelectronics 社製 M93S46等)を用いて、PC Iコンフィギュレーションレジスタとモードレジスタの一部をリセット解除時に初期化する事ができます。EENが"1"のとき、ZEN7251G はリセット解除後ただちにEEPROMからPCIコンフィギュレーションレジスタとローカルモードレジスタのデータをリードし、その間、PCIバスからのすべてのアクセスに対しリトライで応答します。

ZEN7251G はEEPROM用のシリアルクロック(ESK)としてPCIバスのクロックを128分周したものを出力します。また、初期 化だけではなく、EEPROMコントロールレジスタを経由してEEPROMの各制御信号を操作し、任意のアドレスのデータをリード/ライトすることもできます。EEPROMの初期化時の基本的なアクセスタイミングは11. 3. を参照してください。 表8にEEPROMのアドレスマップを示します。

#### 表8. EEPROMのアドレスマップ

| EEPROM<br>オフセットアドレス | レジスタ                       | ビット       | EEPROM<br>設定値 |

|---------------------|----------------------------|-----------|---------------|

| 00h                 | 予約                         |           | 0000h         |

| 01h                 | クラスコード(プログラミング【/F)、レビジョンID | ビット[15:0] | 0001h         |

| 02h                 | クラスコード(ベースクラス、サブクラス)       | ビット[15:0] | 0680h         |

| 03h                 | 予約                         |           | 0000h         |

| 04h                 | サブシステムベンダID                | ビット[15:0] | 0000h         |

| 05h                 | サブシステムID                   | ビット[15:0] | 0000h         |

| 06h                 | インタラプトピン、インタラプトライン         | ビット[8]    | 0100h         |

| 07h                 | Max_Lat, Min_Gnt           | ビット[15:0] | 0000h         |

| 08h                 | レンジレジスタ(I/O用)下位ワード         | ビット[15:2] | ffc1h         |

| 09h                 | バンクレジスタ(I/O用)下位ワード         | ビット[15:2] | 0000h         |

| 0ah                 | レンジレジスタ(メモリ用)下位ワード         | ビット[15:3] | 0000h         |

| 0bh                 | レンジレジスタ(メモリ用)上位ワード         | ビット[9:0]  | fffOh         |

| 0ch                 | バンクレジスタ(メモリ用)下位ワード         | ビット[15:4] | 0000h         |

| 0dh                 | バンクレジスタ(メモリ用)上位ワード         | ビット[9:0]  | 0000h         |

| 0eh                 | タイミングコントローハレジスタ下位ワード       | ビット[15:0] | 0000h         |

| Ofh                 | タイミングコントロールレジスタ上位ワード       | ビット[11:0] | 0000h         |

| 10h                 | デバイスコントロールレジスタ下位ワード        | ビット[7:3]  | 0004h         |

| 11h                 | デバイスコントロールレジスタ上位ワード        | ビット[15:8] | 0000h         |

| 12h                 | I/Oポートコントロールレジスタ下位ワード      | ビット[15:0] | ffOOh         |

| 13~1fh              | 予約                         |           | 0000h         |

| 20~3fh              | ユーザ利用領域                    |           |               |

<sup>※</sup>設定値は各レジスタのリセット値を設定した場合のサンプルです。

# 6. PCIバスアクセス

# 6.1. 対応PCIコマンド

#### 6.1.1. ターゲットアクセス

表9にターゲット動作時の各バスコマンドについての対応を示します(表中の〇印のついているものをサポートしています)。

表9. バスコマンド対応一覧表

| サイクル               | 命令               |        | バスコマンド |        |        |         |  |

|--------------------|------------------|--------|--------|--------|--------|---------|--|

| 9-1570             | म् गुम           | C/BE#3 | C/BE#2 | C/BE#1 | C/BE#0 | サポート    |  |

| I/O                | I/Oリード           | 0      | 0      | 1      | 0      | 0       |  |

| サイクル               | 1/0ラ仆            | 0      | 0      | 1      | 1      | 0       |  |

|                    | メモリリード           | 0      | 1      | 1      | 0      | 0       |  |

| メモリ                | メモリリードライン※1      | 1      | 1      | 1      | 0      | $\circ$ |  |

| サイクル               | メモリリードマルチプル※1    | 1      | 1      | 0      | 0      | $\circ$ |  |

| 9-15/2             | メモリライト           | 0      | 1      | 1      | 1      | 0       |  |

|                    | メモリライト&インバリデート※2 | 1      | 1      | 1      | 1      | 0       |  |

| CFG <sup>**3</sup> | コンフィギュレーションリード   | 1      | 0      | 1      | 0      | $\circ$ |  |

| サイクル               | コンフィギュレーションライト   | 1      | 0      | 1      | 1      | $\circ$ |  |

| インタラプトアク           | ノリッジサイクル         | 0      | 0      | 0      | 0      | ×       |  |

| スペシャルサイ            | クル               | 0      | 0      | 0      | 1      | ×       |  |

| デュアルアドレン           | スサイクル            | 1      | 1      | 0      | 1      | ×       |  |

| 予約                 |                  | 0      | 1      | 0      | 0      | ×       |  |

|                    |                  | 0      | 1      | 0      | 1      | ×       |  |

| 1.氷カ               |                  | 1      | 0      | 0      | 0      | ×       |  |

|                    |                  | 1      | 0      | 0      | 1      | X       |  |

- ※1 メモリリードサイクルとして動作します。

- ※2 メモリライトサイクルとして動作します。

- ※3 CFG=コンフィギュレーション

表9のサポートしていないバスコマンドによるアクセス(網掛け部分)が発生した場合、**ZEN7251G** はDEVSEL#をアサートしません(マスタに対して応答しません)ので、結果的にマスタアボートとなります。

#### 6.1.2. DMA

表10にDMA動作時の各バスコマンドについての対応を示します(表中の〇印のついているものをサポートしています)。

表10. バスコマンド対応一覧表

| サイクル     | 命令             |        | サポート   |        |        |         |

|----------|----------------|--------|--------|--------|--------|---------|

| 9/19/10  | प्राप्त        | C/BE#3 | C/BE#2 | C/BE#1 | C/BE#0 | リハート    |

| I/O      | I/Oリード         | 0      | 0      | 1      | 0      | ×       |

| サイクル     | 1/0ラ仆          | 0      | 0      | 1      | 1      | ×       |

|          | メモリリード         | 0      | 1      | 1      | 0      | 0       |

| メモリ      | メモリリードライン      | 1      | 1      | 1      | 0      | ×       |

| サイクル     | メモリリードマルチプル    | 1      | 1      | 0      | 0      | ×       |

| 9-1570   | メモリライト         | 0      | 1      | 1      | 1      | $\circ$ |

|          | メモリライト&インバリデート | 1      | 1      | 1      | 1      | ×       |

| CFG      | コンフィギュレーションリード | 1      | 0      | 1      | 0      | ×       |

| サイクル     | コンフィギュレーションライト | 1      | 0      | 1      | 1      | ×       |

| インタラプトアク | ノリッジサイクル       | 0      | 0      | 0      | 0      | ×       |

| スペシャルサイ  | クル             | 0      | 0      | 0      | 1      | ×       |

| デュアルアドレン | スサイクル          | 1      | 1      | 0      | 1      | ×       |

|          |                |        | 1      | 0      | 0      | X       |

| 予約       |                | 0      | 1      | 0      | 1      | ×       |

| 1.34.3   | 1、北九           |        | 0      | 0      | 0      | ×       |

|          |                | 1      | 0      | 0      | 1      | ×       |

### 6.2. ディレイド・リード

PCIからのリード・コマンドは常にディレイド・リードとして処理されます。すなわち、マスタからのリード要求に対して、リトライで 応答し、その間にローカルからデータをリードします。このとき、プリフェッチ不可であれば、1個のデータをリードするとただちに ローカルのアクセスは終了します。結果としてプリフェッチ不可ではPCIのバースト転送は行われません。プリフェッチ可能の場合はモードレジスタの設定個数分(8/16/24/32)データ送信用バッファ(TX\_FIFO)に継続してデータをリードします。T X\_FIFO内にいくつデータが格納されるとリード・コマンドに対して応答するかはデバイスコントロールレジスタのbit[4]の値により決まります(10.2.2.9.の表38を参照してください)。ローカルのリード動作が終了するのはTX\_FIFOが空になってディスコネクトした場合かマスタがトランザクションを終了させた場合です。

### 6.3. ポスティッド・ライト

PCIからのライトコマンドは常にポスティッド・ライトとして処理されます。データ受信用バッファ(RX\_FIFO)にデータが存在する間、ローカルに対してライト動作を継続します。RX\_FIFOがエンプティになるとローカルへのアクセスを終了します。RX\_FIFOがフルになるとPCIのトランザクションをディスコネクトします(トランザクションの最初からRX\_FIFOがフルの場合はリトライ)。また、ディレイド・リードのリトライ待機中(ローカルからのリードは完了)にもライトコマンドは受け付けられ、通常の処理が行われます。

# 6.4. 例外処理

#### 6.4.1. ターゲットアクセス

表11にターゲット動作時の例外処理についての対応を示します。

表11. 例外処理とその対応

| 例外内容                | 発生時の対応・処理                                |

|---------------------|------------------------------------------|

|                     | 当該サイクルが ZEN7251G へのものと判断された場合はターゲットアボート、 |

|                     | それ以外の場合はサイクルに応答しません(結果的にマスタアボートとなりま      |

| アドレスパリティーエラー        | す)。                                      |

|                     | コンフィギュレーションレジスタの「パリティエラー応答ビット」、「システムエラー  |

|                     | 応答ビット」の両方が有効になっていればSERR#をアサートします。        |

| データパリティーエラー         | コンフィギュレーションレジスタの「パリティエラー応答ビット」が有効になってい   |

| (ライトアクセス時)          | ればPERR#をアサートします。ただし、バスサイクルはそのまま継続します。    |

| PERR#を検出            | 通常動作を継続します。                              |

| (リードアクセス時にマスタがアサート) |                                          |

| 処理できないバスコマンドを受信     | サイクルに応答しません(結果的にマスタアボートとなります)。           |

| 処理できないアドレスとバイトレーンのパ | ターゲットアボートします(データ処理はおこないません)。             |

| ターンを受信              |                                          |

#### 6.4.2. DMA

表12にDMA動作時の例外処理についての対応を示します。

表12. 例外処理とその対応

| 例外内容                                | 発生時の対応・処理                               |

|-------------------------------------|-----------------------------------------|

| ターゲット未応答                            | マスタアボートします。コンフィギュレーションレジスタの「システムエラー応答   |

|                                     | ビット」が有効になっていればSERR#をアサートします。            |

|                                     | コンフィギュレーションレジスタの「パリティエラー応答ビット」が有効になってい  |

| データパリティーエラー                         | ればPERR#をアサートします。また、コンフィギュレーションレジスタの「マスタ |

| (リードアクセス時)                          | データパリティエラー検出ビット」をセットします。ただし、バスサイクルはそのま  |

|                                     | ま継続します。                                 |

| PERR#を検出                            | コンフィギュレーションレジスタの「パリティエラー応答ビット」が有効になってい  |

| PERR#を検口<br>  (ライトアクセス時にターゲットがアサート) | れば、コンフィギュレーションレジスタの「データパリティエラー検出ビット」を   |

|                                     | セットします。ただし、バスサイクルはそのまま継続します。            |

### 6.5. ディスコネクト

#### 6.5.1. ターゲットアクセス

ターゲットライトアクセスにおいてRX\_FIFOがフルになった場合、または、ターゲットリードアクセスにおいてTX\_FIFOがエンプティになった場合 ZEN7251G はディスコネクトします。11. 1. 14. 及び11. 1. 15. を参照してください。

#### 6.5.2. DMA

DMA転送中に転送先のターゲットデバイスがディスコネクトで応答した場合、ZEN7251Gはいったん転送を終了した後、自動的に再開します。

#### 6.6. リトライ

#### 6.6.1. ターゲットアクセス

ZEN7251G はターゲットアクセスに関して、以下の場合にJトライで応答します。

- ・EEPROMから初期化データをロードしている期間中のすべてのアクセス

- ・ローカルターゲットリードアクセス

**ZEN7251G** はPCIのローカルへのターゲットリードアクセスを受け付けるとローカルバスのリード動作を開始します。このローカルバスのリード動作が完了し、PCIのターゲットリードアクセスに対してデータが準備できるまで **ZEN7251G** はリトライで応答し続けます。11. 1. 13. を参照してください。

・ローカルターゲットライトアクセス

ZEN7251G は同じ種類のローカルへのターゲットライトアクセスを連続して処理することはできません。つまり、ローカルで I/Oライト動作を実行中にさらにPCIのターゲットI/Oライトアクセスを受け付けたとき及びローカルでメモリライト動作を実行中にさらにPCIのターゲットメモリライトアクセスを受け付けたときにはローカルの処理が終了するまでリトライで応答し続けます。11. 1. 12. を参照してください。

モードレジスタターゲットアクセス(ライト/リードとも)

**ZEN7251G** はローカルで何らかの処理を実行中にモードレジスタへのアクセスを受け付けると、ローカルの処理が終了するまでリトライで応答し続けます。

#### 6.6.2. DMA

DMA転送時、転送先のターゲットデバイスがリトライで応答した場合、ZEN7251G はターゲットデバイスがアクセスを受け付けるまで転送を試み続けます。

# 7. ローカルアクセス

### 7.1. 概要

ZEN7251G はPCレベス上のアドレスをローカルアドレスに変換して出力します。ローカル側に最大64Mbyteのメモリ空間と、64KbyteのI/O空間を持つことができますので、メモリアクセス時にはLADR[25:2]、I/Oアクセス時にはLADR[15:2]が有効になります。また、I/Oアクセス時には内蔵アドレスデコーダを有効にすることによって、アドレスの上位8ビットをローカルI/O空間のチップイネーブル信号(LCE#[7:0])にすることができます。

LAS#はローカルアクセスの開始を示します。また、ローカルデバイスのI/O空間、メモリ空間に対するアクセスはLAI/LAM#によって決まります(表13参照)。

なお、LADR[25:2]はいかなる場合にも<u>ハイインピーダンスにはなりません</u>ので、ローカル上でアドレスバスをドライブする他のデバイス(CPU等)と共存することはできません。

表13. ローカルアクセスの発生一覧

| 信号   |          | タイミング                     |                       |      |            |

|------|----------|---------------------------|-----------------------|------|------------|

| LAS# | LAI/LAM# | LADR[25:18]/<br>LCE#[7:0] | コントロールレジスタ<br>bit[27] | アクセス | 備考         |

| 0    | 0        | LADR[25:18]               | X                     | メモリ  |            |

| 0    | 1        | LCE#[7:0]                 | 1                     | I/O  | I/O空間の分割あり |

| 0    | 1        | すべて"1"                    | 0                     | I/O  | I/O空間の分割無し |

| 1    | 1        | _                         | X                     | _    |            |

#### 7.2. ローカルI/Oアクセス

**ZEN7251G** はLAS#、LAI/LAM#、IOW#、IOR#、LADR[25:18]/LCE#[7:0]、LADR[15:2]、LDAT[31:0]、WAIT#の各端子を使用することによってI/Oアクセスを行います。タイミングコントロールレジスタのI/Oチップセレクトイネーブル(bit[27])を"1"にすると、ローカルI/O空間を8個に分割することが可能となります。このとき、ローカルアドレスの上位8ビットは分割したI/O空間のチップイネーブル信号として出力されます。I/Oチップセレクトイネーブルが"0"のとき、LADR[25:18]/LCE#[7:0]には全ビット"1"が出力されます。

表14. ローカルチップイネーブルのデコード範囲

| ローカルアドレス<br>LADR[X+2:X] |     |   |   | ŗ |   | プイネーブ <i>)</i><br>‡[7:0] | V |   |   |   |

|-------------------------|-----|---|---|---|---|--------------------------|---|---|---|---|

| X+2                     | X+1 | X | 7 | 6 | 5 | 4                        | 3 | 2 | 1 | 0 |

| 0                       | 0   | 0 | 1 | 1 | 1 | 1                        | 1 | 1 | 1 | 0 |

| 0                       | 0   | 1 | 1 | 1 | 1 | 1                        | 1 | 1 | 0 | 1 |

| 0                       | 1   | 0 | 1 | 1 | 1 | 1                        | 1 | 0 | 1 | 1 |

| 0                       | 1   | 1 | 1 | 1 | 1 | 1                        | 0 | 1 | 1 | 1 |

| 1                       | 0   | 0 | 1 | 1 | 1 | 0                        | 1 | 1 | 1 | 1 |

| 1                       | 0   | 1 | 1 | 1 | 0 | 1                        | 1 | 1 | 1 | 1 |

| 1                       | 1   | 0 | 1 | 0 | 1 | 1                        | 1 | 1 | 1 | 1 |

| 1                       | 1   | 1 | 0 | 1 | 1 | 1                        | 1 | 1 | 1 | 1 |

表 15. I/O空間のデコード範囲

| I/Oチップセレクト |              | ローカルアドレス |             |          |          |                  |  |  |

|------------|--------------|----------|-------------|----------|----------|------------------|--|--|

| (E         | (ビット[26:24]) |          | LADR[X+2:X] |          |          | I/O空間の分割         |  |  |

| 26         | 25           | 24       | X+2         | X+1      | X        |                  |  |  |

| 0          | 0            | 0        | LADR[8]     | LADR[7]  | LADR[6]  | 64バイト×8個= 512バイト |  |  |

| 0          | 0            | 1        | LADR[9]     | LADR[8]  | LADR[7]  | 128バイト×8個= 1Kバイト |  |  |

| 0          | 1            | 0        | LADR[10]    | LADR[9]  | LADR[8]  | 256バイト×8個= 2Kバイト |  |  |

| 0          | 1            | 1        | LADR[11]    | LADR[10] | LADR[9]  | 512バト×8個= 4Kバイト  |  |  |

| 1          | 0            | 0        | LADR[12]    | LADR[11] | LADR[10] | 1Kバイト×8個= 8Kバイト  |  |  |

| 1          | 0            | 1        | LADR[13]    | LADR[12] | LADR[11] | 2Kバイト×8個= 16Kバイト |  |  |

| 1          | 1            | 0        | LADR[14]    | LADR[13] | LADR[12] | 4Kバイト×8個= 32Kバイト |  |  |

| 1          | 1            | 1        | LADR[15]    | LADR[14] | LADR[13] | 8Kババ×8個= 64Kババ   |  |  |

#### 7.3. ローカルメモリアクセス

ZEN7251G はLAS#、LAI/LAM#、MEW#、MER#、LADR[25:2]、LDAT[31:0]、WAIT#の各端子を使用することによってメモリアクセスを行います。アクセスはローカルI/Oアクセスとほぼ同様ですが異なる点は、LAI/LAM#がメモリアクセスの間"0"になります。なお、ローカルI/O空間のような空間分割機能はなく、ローカルアドレスの全ての端子(LADR [25:2])が1つのメモリ空間のアドレッシングに使用されます。

#### 7.4. アドレッシング(バンクレジスタ)

ZEN7251G はモードレジスタのバンクレジスタを使用することによって、PCIコンフィギュレーションレジスタのローカルバスコントロールBAR<sup>※6</sup>で確保された領域よりも大きな領域を使用することができます。リセット時の設定をそのまま利用する場合、ローカル側に確保できる空間はメモリ空間1Mbyte、I/O空間64byteです。それ以上の空間を使用したい場合、バンクレジスタにアクセスして上位アドレスを設定します。例えば1Mbyteのメモリ領域を確保し、メモリアクセス用バンクレジスタ(Adr. 10h) に03A00000hを設定したとすると、下位18bitはPCIバスのアドレスがそのまま出力され、上位6bitはバンクレジスタの値が出力されます。

LADR[25:20] = 3Ah

LADR[19:2] = AD[19:2](PCIバスのアドレスがそのまま出力される)

このとき、仮にバンクレジスタにO3AFCDO0hを設定したとしても出力されるアドレスは上記と同じになります。バンクレジスタの設定値が有効なのはあくまでBARで確保されたアドレスよりも上位に限られます。

※6 BAR=Base Address Registerの略

#### 7.5. タイミングコントロール

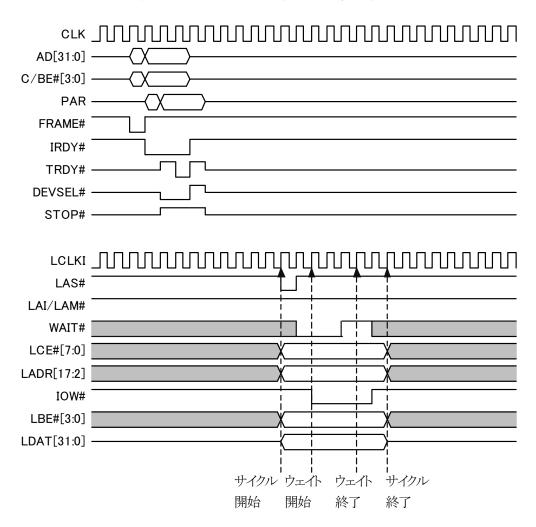

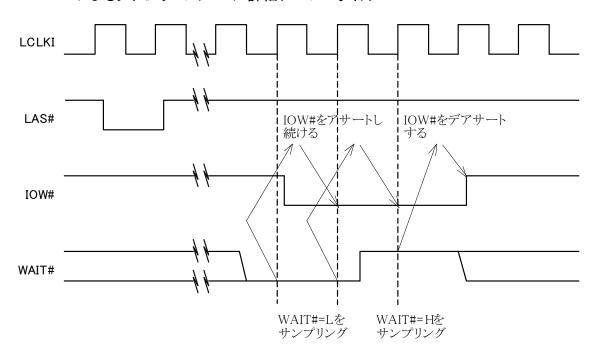

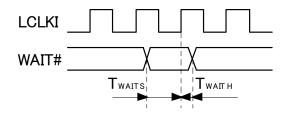

ZEN7251G はモードレジスタとWAIT#によって固定/可変のアクセスサイクルを選択することができます。固定サイクルはタイミングコントロールレジスタに設定値を書き込むことによって行います。可変サイクルはリード/ライトのストローブ信号のタイミングをWAIT#によってコントロールします。

また、WAIT#を利用する場合でも、アドレスセットアップ及びアドレスホールドのタイミングはタイミングコントロールレジスタの設定値に従います。WAIT#サイクルを挿入するときは、LAS#がアサートされてからストローブ信号(IOR#/IOW#/MER#/MEW#)がアサートされるまでにWAIT#を"0"にします。WAIT#はデバイスコントロールレジスタによって有効・無効が決まります。デバイスコントロールレジスタのWAIT#イネーブル(bit[1])が"1"のとき、WAIT#は有効になります。WAIT#を使ったアクセスを行うときは必ずこのビットを"1"にしてください。なお、このビットが"1"のとき、タイミングコントロールレジスタのメモリアクセスパルスワイズ(bit[19:16])及びI/Oアクセスパルスワイズ(bit[7:4])の設定値は無効になります。11. 1. 6. ~11. 1. 11. を参照してください。

# 7.6. リードプリフェッチ(メモリアクセス)

ローカルメモリ領域へのリードアクセスに関して、プリフェッチ動作を行うことができます。プリフェッチを有効にするにはデバイスコントロールレジスタのbit[7]に"1"を設定します。プリフェッチが有効なとき、**ZEN7251G** はPCIのメモリリードコマンドを受け付けるとデバイスコントロールレジスタのbit[6:5]で決まる数だけのデータを連続してリードしTX\_FIFOに格納します。こうすることによってPCIのアクセスがバーストリードを要求した際、効率的に転送できます。11. 1. 5. を参照してください。

また、同レジスタのbit[4]で、プリフェッチ有効時TX\_FIFO内にどれだけデータが存在するとPCIのターゲットリードを受け付けるかを決めることができます。このビットが"0"のとき、データが1個でもTX\_FIFOに存在するとPCIのアクセスを受け付けます。"1"のときはTX\_FIFO内のデータがプリフェッチ設定数の1/2になるとリード・コマンドを受け付けます。

#### 8. DMA

#### 8.1. 概要

**ZEN7251G** は1チャネルのDMA機能を内蔵しています。これにより、ホストCPUの負荷を減らして高速なホスト←→ターゲットボード間の転送を実現しています。DMA転送時のデータバッファとしてPCI to ローカル(DRX\_FIFO)とローカル to PCI(DTX FIFO)のそれぞれに独立した32段のFIFOを装備しています。

また、ZEN7251G はDMA転送に必要なレジスタ群(PCIスタートアドレス、ローカルスタートアドレス及び転送回数)を4セット独立して装備しています。DMA・転送コントロールレジスタの設定により、最大4つの非連続な領域への転送を1回のDMA起動で行うことが可能です(リレー転送)。

なお、ローカルバスの基本的な転送方式はターゲットアクセスと同じ、インタフェース設計の容易なストローブ方式です。

#### 8.2. 転送回数

DMAの転送回数はDMA・転送回数レジスタに設定します(8.8.のリレー転送のために4セット分あります)。転送設定回数はLWord単位での設定になります。

### 8.3. 転送領域

PCIバス側はメモリ固定、ローカルバス側はI/Oとメモリから選択可能です。DMA・転送コントロールレジスタのbit[25]が "0"のときメモリ領域、"1"のときI/O領域に転送します。

#### 8.4. 転送方向

DMA・転送コントロールレジスタのbit[24]が"0"のときローカル to PCI転送、"1"のときPCI to ローカル転送を行います。

### 8.5. バースト長(PCIバス)

転送方向及び転送領域に関わらず、DMA時 ZEN7251G はDMA・転送コントロールレジスタのbit[30:28]で決まる長さのバースト転送を行います。 ZEN7251G はPCレバスの過度の占有を避けるため、常にこの設定数分だけデータを転送するといったんバースト転送を終了します。 従って、最大でも一度に24データを超えるバースト転送は行いません。 例えば転送回数を100回にバースト長を24に設定した場合、24バースト4回と4バースト1回の計5回の転送に自動的に分割されます。

なお、ローカルバス側はPCI to ローカルの場合はDRX\_FIFOにデータが1つでもあれば、また、ローカル to PCIの場合はDTX\_FIFO内に空きが1つでもあればただちに転送を開始します。

#### 8.6. アドレッシング

PCIバスの転送スタートアドレスはDMA・PCIスタートアドレスレジスタに、ローカルバスの転送スタートアドレスはDMA・ローカルスタートアドレスレジスタに設定します(8.8.0)ルー転送のためにそれぞれ4セット分あります)。 通常、PCI/ローカルともアドレスはデータの転送に伴ってインクリメントしていきますが、ローカルアドレスについてはDMA・ローカルスタートアドレスレジスタのbit[31]を"1"に設定することでスタートアドレスを固定して出すことができます。なお、スタートアドレス設定レジスタのbit幅はPCIバス側32bit、ローカルバス側24bit (ただし、転送領域がI/Oの場合は下位16bitのみ有効)です。

また、I/O領域への転送の場合、ターゲットアクセスと同じように内蔵アドレスデコーダを使用することも可能です。

#### 8.7. 起動/終了

#### 8.7.1. 通常起動/通常終了

DMA・転送コントロールレジスタのbit[31]に"1"をライトすることによりDMA転送が起動します。このビットはあらかじめ設定された個数分のデータを転送すると自動的に"0"になり転送を終了します。

#### 8.7.2. 強制終了

DMA転送中にDMA・転送コントロールレジスタのbit[31]に"0"をライトすると転送を終了します。

#### 8.7.3. ターゲットアボート

DMA・エラーコントロールレジスタのbit[1]に"1"が設定されている場合、DMA転送中にターゲットアボートが発生すると転送を終了します。

#### 8.7.4. マスタアボート

DMA・エラーコントロールレジスタのbit[0]に"1"が設定されている場合、DMA転送中にマスタアボートが発生すると転送を終了します。

## 8.8. リレー転送

ZEN7251G はDMA・PCIスタートアドレスレジスタ、DMA・ローカルスタートアドレスレジスタ及びDMA・転送回数レジスタを4セット持っています。転送パターンは以下の4通りがあり、DMA・転送コントロールレジスタのbit[27:26]の設定に従います。本機能を利用することにより、ホストあるいはローカルの非連続な領域に一度のDMA起動で転送を完了させることが可能になります。また、DMA・転送コントロールレジスタのbit[1:0]をリードすることによって、現在どのセットを転送中かモニタすることも可能です。

表16. DMA転送セット設定

| DMA・転送コントロールレジスタbit[27:26] | 有効DMA転送セット      |

|----------------------------|-----------------|

| 00                         | 1st             |

| 01                         | 1st→2nd         |

| 10                         | 1st→2nd→3rd     |

| 11                         | 1st→2nd→3rd→4th |

# 9. その他の機能

#### 9.1. 汎用I/Oポート

ZEN7251GはI/Oポートコントロールレジスタの設定によって入力及び出力として利用できる汎用ポートを8本装備しています。なお、ポートの方向設定及び出力ポート時の初期値はEEPROMで設定することもできます(ポートの出力値はEEPROMによるすべてのレジスタの初期化が完了するまで不定です)。

#### 9.2. PCIクロックタイマ

**ZEN7251G** は32bitのPCIクロックタイマ(フリーラン・ダウンカウンタ)とカウンタの周期を決めるためのPCIクロックタイマレジスタを装備しています。カウンタに値をロードするには、まず、PCIクロックタイマロードレジスタに値を設定し、その後、デバイスコントロールレジスタのbit[0]に"1"をライトします。設定値をロードした後、デバイスコントロールレジスタのbit[1]を"1"にするとカウントダウンを開始します。9. 3. 2. のPCIクロックタイマ割り込みを有効にしている場合、カウント値がOhになると割り込みが発生します。なお、カウンタは値がOhになると自動的にロードレジスタから値をロードしなおし、ダウンカウントを継続します。クロックタイマイネーブルビットに"0"をライトしない限りこの動作を繰り返します。

### 9.3. 割り込み

ZEN7251G は次の3つの要因によってPCIバスの割り込み信号であるINTA#をアサートすることができます。外部割り込み要因であるIRQ#についてはマスクすることができます。また、内部割り込み要因であるPCIクロックタイマおよびDMA転送終了については有効/無効の設定が可能です。

#### 9.3.1. IRQ#

ローカルバス側の割り込み信号IRQ#をそのままINTA#に出力します。インタラプトコントロールレジスタのbit[3]によりマスクすることもできます。なお、本割り込みをマスク中にIRQ#が"0"になり、その状態のままマスクを解除した場合はただちにINTA#がアサートされます。

#### 9.3.2. PCIクロックタイマ

PCIクロックタイマの値がOhになった時点でINTA#を出力します。レジスタ設定により有効/無効を選択できます。なお、本割り込みを無効設定にしているあいだに割り込み要因が発生し、その後本割り込みを有効に再設定してもただちにINTA#がアサートされることはありません。

#### 9.3.3. DMA転送終了

DMA転送が終了した時点でINTA#を出力します。レジスタ設定により有効/無効を選択できます。なお、本書的込みを無効設定にしているめいだに割り込み要因が発生し、その後本割り込みを有効に再設定してもただちにINTA#がアサートさ

れることはありません。

## 9.4. デバッグ用アドレスマッチ信号

AD\_MATCH(端子番号F1)はPCIアクセスが ZEN7251G のいずれかのベースアドレスとマッチするとアサートされます。本信号端子は ZEN7251G を搭載したPCIボードのデバッグ用に用意しています。ローカル側のアクセスが期待通りに動作しない場合、本端子を観測することで原因の切り分けが可能です。本信号端子がアサートされていれば、ZEN7251G は少なくともそのときのPCIのトランザクションを自分に対するものとして処理しています。逆にアサートされない場合は、ホスト上のソフトに何か問題があるものと推定されます(ZEN7251G にセットされているベースアドレスとソフトで指定しているアドレスが一致していない等)。

なお、本端子はデバッグ用ですのでテストピンとして引き出しておき、実動作時のローカルデバイスのコントロール等には使用しないことを推奨いたします。

# 10. レジスタ

# 10.1. PCIコンフィギュレーションレジスタ

## 10.1.1. レジスタマップ

表17に**ZEN7251G**のPCIコンフィギュレーションレジスタのアドレスマップを示します。なお、表中の網掛け部分はサポートしていません。

表17. PCIコンフィギュレーションレジスタ

|        | ,       |             |               |             |  |  |

|--------|---------|-------------|---------------|-------------|--|--|

| オフセット  |         | Ľ)          | ット            |             |  |  |

| アドレス   | 31 24:  | 23 16       | 15 87         | 7 0         |  |  |

| 00h    | デバ      | クID         | ~>/           | Я́Ю         |  |  |

| 04h    | ステータ    | スレジスタ       | コマンド          | レジスタ        |  |  |

| 08h    |         | クラスコード      |               | レビジョンID     |  |  |

| 0ch    | BIST    | ヘッダタイプ      | マスタレイテンシタイマ   | キャッシュラインサイズ |  |  |

| 10h    |         | モードレジスタコントロ | ューノレBAR(I/O用) |             |  |  |

| 14h    |         | ローカルバスコントロ  | ールBAR(I/O用)   |             |  |  |

| 18h    |         | ローカルバスコントロ  | ールBAR(メモリ用)   |             |  |  |

| 1ch    |         | 予           | 約             |             |  |  |

| 20h    |         | 予           | <u></u> 約     |             |  |  |

| 24h    |         | 予           | 約             |             |  |  |

| 28h    |         | カードバス CIS   | ポインタレジスタ      |             |  |  |

| 2ch    | サブシ     | ステムID       | サブシステ、        | ムベンダID      |  |  |

| 30h    |         | エクスパンジョン    | ∕ROM BAR      |             |  |  |

| 34h    | 予約      |             |               |             |  |  |

| 38h    | 予約      |             |               |             |  |  |

| 3ch    | Max_Lat | Min_Gnt     | インタラプト端子      | インタラプトライン   |  |  |

| 40∼ffh |         | 予           | 約             |             |  |  |

### 10.1.2. レジスタ一覧

表18~表28にPCIコンフィギュレーションレジスタの詳細について示します。また、表の見方は、

ビット: ビットポジションです。名称: 該当ビットの名称です。機能: 該当ビットの機能です。

リセット値: リセット状態の値を示しています。左上がMSBとなり、以降右下に向かってLSBとなります。

R : リードの可否を示しています( $\bigcirc$ →可能、 $\times$ →不可)。 W : ライトの可否を示しています( $\bigcirc$ →可能、 $\times$ →不可)。

I : EEPROMによる初期化の可否を示しています( $\bigcirc$ →可能、 $\times$ →不可)。

となっています。また、これは10.2.節も同様です。

#### 10.1.2.1. デバイスID & ベンダID[Adr. OOh]

#### 表18. デバイスID & ベンダID

| ı | ビット   | 名称       | 機能                             | リセット値    | R       | W | Ι |

|---|-------|----------|--------------------------------|----------|---------|---|---|

|   | 21.16 | デバイスID   | ZENIC が製造した ZEN7251G を識別するためのI | 01110010 |         | ~ |   |

|   | 31:16 |          | D(7251h)です。                    | 01010001 | 1010001 |   |   |

|   | 15.0  | ベンダID    | PCI SIGによって割り当てられた ZENIC を示すID | 00101110 |         | > | _ |

|   | 15:0  | · ~ ク ID | (2EC1h)です。                     | 11000001 |         | ^ | ^ |

# 10.1.2.2. ステータス & コマンド[Adr. O4h]

## 表19. ステータス & コマンド

| ビット   | 名称                       | 機能                                                                                                                      | リセット値  | R       | W       | Ι |

|-------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|--------|---------|---------|---|

| 31    | パリティエラー検知                | パリティエラーを検知したとき"1"になります。"1"を<br>書き込むと"0"にクリアされます。                                                                        | 0      | 0       | 0       | X |

| 30    | システムエラー通報                | システムエラーが発生したとき"1"になります。"1"を書き込むと"0"にクリアされます。                                                                            | 0      | 0       | 0       | × |

| 29    | マスタアボート受信                | DMA中にマスタアボートが発生したとき"1"になり<br>ます。"1"を書き込むと"0"にクリアされます。                                                                   | 0      | 0       | 0       | × |

| 28    | ターゲットアボート受信              | DMA中にターゲットアボートが発生したとき"1"になります。"1"を書き込むと"0"にクリアされます。                                                                     | О      | 0       | 0       | × |

| 27    | ターゲットアボート通報              | ターゲットアクセス中にターゲットアボートが発生したとき"1"になります。"1"を書き込むと"0"にクリアされます。                                                               | 0      | 0       | 0       | × |

| 26:25 | DEVSEL#タイミング             | ターゲットがDEVSEL#をアサートするタイミングを<br>示しています。                                                                                   | 01     | 0       | ×       | × |

| 24    | データパリティーエラー<br>検知        | コマンドレジスタのパリティエラー応答ビットが"1"<br>で、かつ、DMA中に <b>ZEN7251G</b> かターゲットデバ<br>イスがPERR#をアサートしたとき"1"になります。<br>"1"を書き込むと"0"にクリアされます。 | 0      | 0       | 0       | × |

| 23    | 高速BTB <sup>※7</sup> 対応可能 | 異なるターゲットデバイスにわたる高速BTBに対応<br>可能なことを示します。                                                                                 | 1      | 0       | ×       | × |

| 22    | 予約                       |                                                                                                                         | 0      | 0       | ×       | X |

| 21    | 66MHzサイクル                | 未サポート                                                                                                                   | 0      | 0       | ×       | X |

| 20:16 | 予約                       |                                                                                                                         | 00000  | 0       | ×       | X |

| 15:10 | 予約                       |                                                                                                                         | 000000 | 0       | X       | X |

| 9     | 高速BTB有効                  | 未サポート                                                                                                                   | 0      | 0       | ×       | X |

| 8     | システムエラー応答                | "1"のとき、SERR#が有効になります。                                                                                                   | 0      | $\circ$ | $\circ$ | X |

| 7     | ウェイトサイクル コントロール          | 未サポート                                                                                                                   | 0      | 0       | ×       | × |

| 6     | パリティエラー応答                | "1"のとき、PERR#が有効にてよります。                                                                                                  | 0      | 0       | 0       | X |

| 5     | VGAパレットスヌープ              | 未サポート                                                                                                                   | 0      | 0       | X       | X |

| 4     | メモリライト<br>&インバリデート       | 未サポート                                                                                                                   | 0      | 0       | ×       | × |

| 3     | スペシャルサイクル                | 未サポート                                                                                                                   | 0      | 0       | X       | X |

| 2     | バスマスタイネーブル               | "1"のとき、マスタとして動作することができます。                                                                                               | 0      | 0       | 0       | × |

| 1     | メモリイネーブル                 | "1"のとき、メモリアクセスに応答することができます。                                                                                             | 0      | 0       | 0       | × |

| 0     | I/Oイネーブル                 | "1"のとき、I/Oアクセスに応答することができます。                                                                                             | 0      | 0       | 0       | × |

<sup>※7</sup> BTB=Back To Backの略

## 10.1.2.3. クラスコード & レビジョンID[Adr. 08h]

#### 表20. クラスコード & レビジョンID

| ビット   | 名称                 | 機能                                                                        | リセット値    | R | W | Ι |

|-------|--------------------|---------------------------------------------------------------------------|----------|---|---|---|

| 31:24 | ベースクラス             | デバイスのベースクラスを分類します。                                                        | 00000110 | 0 | X | 0 |

| 23:16 | サブクラス              | デバイスのサブクラスを分類します。                                                         | 10000000 | 0 | X | 0 |

| 15:8  | プログラミング<br>インタフェース | プログラミングインタフェースについて互換性を備え<br>た業界標準のインタフェースが存在するときに、そ<br>の種類を特定するために使用されます。 | 00000000 | 0 | × | 0 |

| 7:0   | レビジョンID            | デバイスのレビジョンを示すために使用します。                                                    | 00000001 | 0 | X | 0 |

## 10.1.2.4. BIST & ヘッダタイプ & マスタレイテンシタイマ & キャッシュラインサイズ [Adr. Och]

# 表21. BIST & ヘッダタイプ & マスタレイテンシタイマ & キャッシュラインサイズ

| ビット   | 名称                 | 機能                                                                                     | リセット値    | R | W | Ι |

|-------|--------------------|----------------------------------------------------------------------------------------|----------|---|---|---|

| 31    | BISTイネーブル          | 未サポート                                                                                  | 0        | 0 | X | X |

| 30    | BISTスタート           | 未サポート                                                                                  | 0        | 0 | X | X |

| 29:28 | 予約                 |                                                                                        | 00       | 0 | × | × |

| 27:24 | BIST完了コード          | 未サポート                                                                                  | 0000     | 0 | × | × |

| 23    | ヘッダタイプ             | デバイスが単機能デバイスか多機能デバイスのどちらであるのかを示しています。ZEN7251G は単機能デバイスのみをサポートしていますので、このビットは常に"0"となります。 | 0        | 0 | × | × |

| 22:16 | コンフィギュレーションタ<br>イプ | コンフィギュレーションデバイスのヘッダタイプを示しています。 <b>ZEN7251G</b> はPCIデバイスなので"000 0000"となります。             | 0000000  | 0 | × | × |

| 15:8  | マスタレイテンシタイマ        | バスサイクルを中止するまでのタイミングを決定する<br>タイマです。下位3bitは"0"固定です。                                      | 00000000 | 0 | 0 | × |

| 7:0   | キャッシュラインサイズ        | 未サポート                                                                                  | 00000000 | 0 | X | X |

#### 10.1.2.5. モードレジスタコントロールBAR(I/O用)[Adr. 10h]

#### 表22. モードレジスタコントロールBAR(I/O用)

| ビット  | 名称                   | 機能                                                                                            | リセット値                                 | R | W | Ι |

|------|----------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|---|---|---|

| 31:7 | モードレジスタ<br>コントロールBAR | モードレジスタにI/Oアクセスするためのアドレスを<br>示しています。                                                          | 11111111<br>11111111<br>11111111<br>1 | 0 | 0 | × |

| 6:2  | モードレジスタ<br>コントロールBAR | モードレジスタにI/Oアクセスするためのアドレスを<br>示しています。モードレジスタは128byteのアドレス<br>空間を使用しますので、ビット[6:2]は"0"となりま<br>す。 | 00000                                 | 0 | × | × |

| 1    | 予約                   |                                                                                               | 0                                     | 0 | X | × |

| 0    | I/Oアクセス<br>インジケータ    | モードレジスタへのI/Oアクセスに応答することを<br>示すビットです。                                                          | 1                                     | 0 | × | × |

#### 10.1.2.6. ローカルバスコントロールBAR(I/O用)[Adr. 14h]

#### 表23. ローカルバスコントロールBAR(I/O用)

| ビット  | 名称                  | 機能                                                                                                       | リセット値                                     | R | W | Ι |

|------|---------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|---|---|---|

| 31:2 | ローカルバス<br>コントロールBAR | ローカルデバイスにI/Oアクセスするためのアドレスを示しています。このレジスタはモードレジスタ内にあるレンジレジスタの値によって決まります。EEPROMを使用しない場合、64byteのI/O空間を確保します。 | 00000000<br>00000000<br>0000000<br>000000 | 0 | 0 | × |

| 1    | 予約                  |                                                                                                          | 0                                         | 0 | X | X |

| 0    | I/Oアクセス<br>インジケータ   | ローカルバスへのI/Oアクセスに応答することを示<br>すビットです。                                                                      | 1                                         | 0 | × | × |

#### 10.1.2.7. ローカルバスコントロールBAR(メモリ用)[Adr. 18h]

#### 表24. ローカルバスコントロールBAR(メモリ用)

| ビット  | 名称                  | 機能                                                                                                       | リセット値                                    | R | W | Ι |

|------|---------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|---|---|---|

| 31:4 | ローカルバス<br>コントロールBAR | ローカルデバイスにメモリアクセスするためのアドレスを示しています。このレジスタはモードレジスタ内にあるレンジレジスタの値によって決まります。EEPROMを使用しない場合、1Mbyteのメモリ空間を確保します。 | 00000000<br>00000000<br>00000000<br>0000 | 0 | 0 | × |

| 3    | プリフェッチ              | この領域がプリフェッチ可能かどうかを示します。<br>"1"のときプリフェッチ可能です。                                                             | 0                                        | 0 | × | × |

| 2:1  | アドレスタイプ             | 未サポート                                                                                                    | 00                                       | 0 | X | X |

| 0    | メモリアクセス<br>インジケータ   | ローカルバスへのメモリアクセスに応答することを示すビットです。                                                                          | 0                                        | 0 | × | × |

#### 10.1.2.8. カードバスCISポインタ[Adr. 28h]

#### 表25. カードバスCISポインタ

| ビット  | 名称                   | 機能    | リセット値                                        | R | W | Ι |

|------|----------------------|-------|----------------------------------------------|---|---|---|

| 31:0 | カードバス<br>CISポインタレジスタ | 未サポート | 00000000<br>00000000<br>00000000<br>00000000 | 0 | × | × |

#### 10.1.2.9. サブシステムID & サブシステムベンダID[Adr. 2ch]

#### 表26. サブシステムID & サブシステムベンダID

| ビッ    | 小          | 名称          | 機能                          | リセット値    | R | W           | Ι |

|-------|------------|-------------|-----------------------------|----------|---|-------------|---|

| 31:16 | 16         | サブシステムID    | ベンダが製造したシステムを識別するためのIDで     | 00000000 |   | ~           |   |

|       | 10         | y / V / AID | す。                          | 00000000 |   | <           |   |

| 15:0  | ٠.         | サブシステムベンダID | ベンダIDと同様に、PCI SIGによって割り当てられ | 00000000 |   | <b>&gt;</b> |   |

|       | リノシヘノム シグロ | たIDです。      | 00000000                    |          |   |             |   |

#### 10.1.2.10. エクスパンジョンROM BAR[Adr. 30h]

#### 表27. エクスパンジョンROM BAR

| ビット             | 名称          | 機能             | リセット値    | R | W | I     |

|-----------------|-------------|----------------|----------|---|---|-------|

| 31:0 エクス<br>BAR |             |                | 00000000 |   |   |       |

|                 | エクスパンジョンROM | 未サポート          | 00000000 |   | ~ | \ \ \ |

|                 | BAR         | <b>米りか 1</b> . | 00000000 |   | ^ |       |

|                 |             |                | 00000000 |   |   |       |

#### 10.1.2.11. Max\_Lat & Min\_Gnt & インタラプトライン & インタラプト端子[Adr. 3ch]

### 表28. Max\_Lat & Min\_Gnt & インタラプト端子 & インタラプトライン

| ビット   | 名称        | 機能                                                                                                                                                                                                                                                                 | リセット値    | R | W | Ι |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|---|---|

| 31:24 | Max_Lat   | ZEN7251G がDMA時、どのくらいの頻度でバスの使用権を必要とするかを表します。                                                                                                                                                                                                                        | 00000000 | 0 | × | 0 |

| 23:16 | Min_Gnt   | ZEN7251G がDMA時、最低実行したいバーストサイクルを表します。                                                                                                                                                                                                                               | 00000000 | 0 | × | 0 |

| 15:8  | インタラプト端子  | コンフィギュレーションによって割り込みがINTA#<br>~INTD#のどのインタラプト信号に接続されるの<br>かを示しています。ZEN7251G は単機能デバイス<br>なのでINTA#を利用します。なお、EEPROMに<br>よる値のロードはbit[8]のみ可能で、bit[15:9]は<br>常に"0"固定です。<br>なお、このbitの設定だけでは ZEN7251G の割り込<br>み機能は有効になりません。割り込みを利用するに<br>はインタラプトコントロールレジスタを設定する必要<br>があります。 | 00000001 | 0 | × | 0 |

| 7:0   | インタラプトライン | コンフィギュレーションによって割り込みがどのインタ<br>ラプトラインに接続されるのかを示します。                                                                                                                                                                                                                  | 00000000 | 0 | 0 | × |

# 10.2. モードレジスタ

ZEN7251G の各種機能はモードレジスタに値を設定することによって制御します。モードレジスタへはコンフィギュレーション レジスタのモードレジスタ用のベースアドレスレジスタを通してI/Oアクセスします。

#### 10.2.1. レジスタマップ

表29に ZEN7251G のモードレジスタのアドレスマップを示します。

| 表29. モードレ | <i>バ</i> ブスタ               |

|-----------|----------------------------|

| オフセット     | ビット                        |

| アドレス      | 31 2423 1615 87 0          |

| 00h       | レンジレジスタ(I/O用)              |

| 04h       | バンクレジスタ(I/O用)              |

| 08h       | 予約                         |

| 0ch       | レンジレジスタ(メモリ用)              |

| 10h       | バンクレジスタ(メモリ用)              |

| 14h       | 予約                         |

| 18h       | タイミングコントロールレジスタ            |

| 1ch       | 予約                         |

| 20h       | I/Oポートコントロールレジスタ           |

| 24h       | 予約                         |

| 28h       | 予約                         |

| 2ch       | インタラプトコントロールレジスタ           |

| 30h       | EEPROMコントロールレジスタ           |

| 34h       | デバイスコントロールレジスタ             |

| 38h       | PCIクロックタイマロードレジスタ          |

| 3ch       | PCIクロックタイマレジスタ             |

| 40h       | 予約                         |

| 44h       | 予約                         |

| 48h       | DMA・転送コントロールレジスタ           |

| 4ch       | DMA・エラーコントロールレジスタ          |

| 50h       | DMA・PCIスタートアドレスレジスタ1stセット  |

| 54h       | DMA・ローカルスタートアドレスレジスタ1stセット |

| 58h       | DMA・転送回数レジスタ1stセット         |

| 5ch       | DMA・PCIスタートアドレスレジスタ2ndセット  |

| 60h       | DMA・ローカルスタートアドレスレジスタ2ndセット |

| 64h       | DMA・転送回数レジスタ2ndセット         |

| 68h       | DMA・PCIスタートアドレスレジスタ3rdセット  |

| 6ch       | DMA・ローカルスタートアドレスレジスタ3rdセット |

| 70h       | DMA・転送回数レジスタ3rdセット         |

| 74h       | DMA・PCIスタートアドレスレジスタ4thセット  |

| 78h       | DMA・ローカルスタートアドレスレジスタ4thセット |

| 7ch       | DMA・転送回数レジスタ4thセット         |

# 10.2.2. レジスタ一覧

#### 10.2.2.1. レンジレジスタ(I/Oアクセス用)[Adr. OOh]

#### 表30. レンジレジスタ(I/O用)

| ビット   | 名称                    | 機能                                                                                                              | リセット値                | R | W | Ι |

|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|---|---|---|

| 31:16 | 予約                    |                                                                                                                 | 11111111<br>11111111 | 0 | × | × |

| 15:2  | ローカルI/Oレンジ            | 必要とするローカルI/O空間のサイズをローカルバスコントロールBARに知らせるためのレジスタです。下位からの連続している"O"のビットがBARで確保するI/O空間を示しています。リセット時64by teの空間を確保します。 | 11111111<br>110000   | 0 | × | 0 |

| 1     | 予約                    |                                                                                                                 | 0                    | 0 | X | X |

| 0     | ローカルI/Oアクセス<br>インジケータ | ローカルデバイスへのI/Oアクセスに応答すること<br>を示すビットです。                                                                           | 1                    | 0 | × | × |

#### 10.2.2.2. バンクレジスタ(I/Oアクセス用)[Adr. O4h]

#### 表31. バンクレジスタ(I/O用)

| ビット   | 名称                 | 機能                                                                                               | リセット値              | R | W | Ι |

|-------|--------------------|--------------------------------------------------------------------------------------------------|--------------------|---|---|---|

| 31:16 | 予約                 |                                                                                                  | 0000000<br>0000000 | 0 | × | × |

| 15:2  | ローカルI/O<br>バンクアドレス | ローカルデバイスへのI/Oアクセスを行うときのアドレスとなります。PCIバス上のアドレスとこのレジスタの値を合成してローカルアドレスとして出力します。<br>詳細は7.4.を参照してください。 | 0000000            | 0 | 0 | 0 |

| 1:0   | 予約                 |                                                                                                  | 00                 | 0 | X | × |

#### 10.2.2.3. レンジレジスタ(メモリアクセス用)[Adr. Och]

#### 表32. レンジレジスタ(メモリ用)

| ビット   | 名称                    | 機能                                                                                                             | リセット値                          | R | W | I |

|-------|-----------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------|---|---|---|

| 31:26 | 予約                    |                                                                                                                | 111111                         | 0 | × | × |

| 25:4  | ローカルメモリレンジ            | 必要とするローカルメモリ空間のサイズをローカルバスコントロールBARに知らせるためのレジスタです。下位からの連続している"0"のビットがBARで確保するメモリ空間を示しています。リセット時1Mbyteの空間を確保します。 | 11111100<br>00000000<br>000000 | 0 | × | 0 |

| 3     | プリフェッチ                | この領域がプリフェッチ可能かどうかを示します。<br>"1"のときプリフェッチ可能です。                                                                   | 0                              | 0 | × | 0 |

| 2:1   | 予約                    |                                                                                                                | 00                             | 0 | × | × |

| 0     | ローカルメモリアクセス<br>インジケータ | ローカルデバイスへのメモリアクセスに応答すること<br>を示すビットです。                                                                          | 0                              | 0 | × | × |

## 10.2.2.4. バンクレジスタ(メモリアクセス用)[Adr. 10h]

### 表33. バンクレジスタ(メモリ用)

| ビット   | 名称              | 機能                                                                                               | リセット値                          | R | W | Ι |

|-------|-----------------|--------------------------------------------------------------------------------------------------|--------------------------------|---|---|---|

| 31:26 | 予約              |                                                                                                  | 000000                         | 0 | X | X |

| 25:4  | ローカルメモリ バンクアドレス | ローカルデバイスへのメモリアクセスを行うときのアドレスとなります。PCIバス上のアドレスとこのレジスタの値を合成してローカルアドレスとして出力します。<br>詳細は7.4.を参照してください。 | 00000000<br>00000000<br>000000 | 0 | 0 | 0 |

| 3:0   | 予約              |                                                                                                  | 0000                           | 0 | × | × |

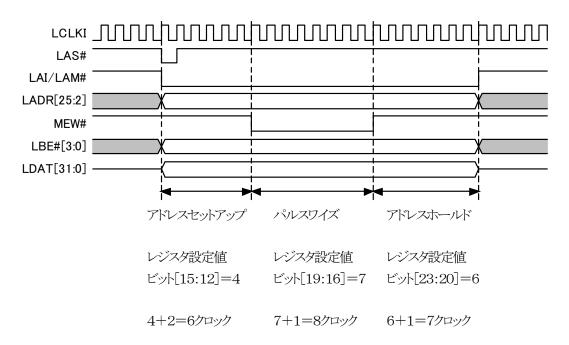

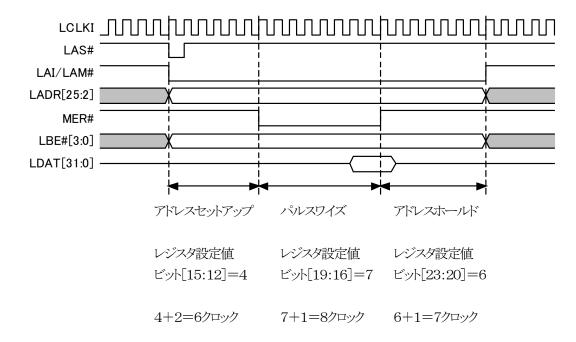

### 10.2.2.5. タイミングコントロールレジスタ[Adr. 18h]

### 表34. タイミングコントロールレジスタ

| ビット   | 名称                        | 機能                                                                                       | リセット値 | R | W | Ι |

|-------|---------------------------|------------------------------------------------------------------------------------------|-------|---|---|---|

| 31:28 | 予約                        |                                                                                          | 0000  | 0 | X | × |

| 27    | 内蔵アドレスデコーダ<br>イネーブル       | このビットが"1"のとき、内蔵アドレスデコーダが有効になります。                                                         | 0     | 0 | 0 | 0 |

| 26:24 | 内蔵アドレスデコーダ<br>デコードビットセレクト | 内蔵アドレスデコーダがデコード対象とするアドレス<br>のビット位置を選択します。                                                | 000   | 0 | 0 | 0 |

| 23:20 | メモリアクセス<br>アドレスホールド       | メモリアクセスにおけるアドレスホールドのクロック数<br>を設定します。《設定値+1》がアドレスホールドのクロック数となります。                         | 0000  | 0 | 0 | 0 |

| 19:16 | メモリアクセス パルスワイズ            | メモリアクセスにおけるMER#/MEW#のローパルス幅を設定します。《設定値+1》がローパルス幅のクロック数となります。なお、この設定はWAIT#が有効な場合は無効になります。 | 0000  | 0 | 0 | 0 |

| 15:12 | メモリアクセス<br>アドレスセットアップ     | メモリアクセスにおけるアドレスセットアップのクロック数を設定します。《設定値+2》がアドレスホールドのクロック数となります。                           | 0000  | 0 | 0 | 0 |

| 11:8  | I/Oアクセス<br>アドレスホールド       | I/Oアクセスにおけるアドレスホールドのクロック数<br>を設定します。《設定値+1》がアドレスホールドのクロック数となります。                         | 0000  | 0 | 0 | 0 |

| 7:4   | I/Oアクセス<br>パルスワイズ         | I/OアクセスにおけるIOR#/IOW#のローパルス幅を設定します。《設定値+1》がローパルス幅のクロック数となります。なお、この設定はWAIT#が有効な場合は無効になります。 | 0000  | 0 | 0 | 0 |

| 3:0   | I/Oアクセス<br>アドレスセットアップ     | I/Oアクセスにおけるアドレスセットアップのクロック<br>数を設定します。《設定値+2》がアドレスホールド<br>のクロック数となります。                   | 0000  | 0 | 0 | 0 |

## 10.2.2.6. I/Oポートコントロールレジスタ[Adr. 20h]

## 表35. I/Oポートコントロールレジスタ

| ビット   | 名称       | 機能                                         | リセット値              | R | W | Ι |

|-------|----------|--------------------------------------------|--------------------|---|---|---|

| 31:16 | 予約       |                                            | 0000000<br>0000000 | 0 | × | × |

| 15:8  | I/Oポート設定 | 汎用I/Oポートの入出力方向を設定します。"1"で入力、"0"で出力に設定されます。 | 11111111           | 0 | 0 | 0 |

| 7:0   | I/Oポート   | 汎用I/Oポートです。bit[15:8]の設定により入出力の方向を決定します。    | 00000000           | 0 | 0 | 0 |

### 10.2.2.7. インタラプトコントロールレジスタ[Adr. 2ch]

## 表36. インタラプトコントロールレジスタ

| ビット   | 名称                       | 機能                                                                                                                     | リセット値             | R | W | Ι |

|-------|--------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|---|---|---|

| 31:18 | 予約                       |                                                                                                                        | 0000000<br>000000 | 0 | × | × |

| 17    | DMAエラーモニタ<br>(ターゲットアボート) | DMAエラーコントロールレジスタのbit[17]をモニタ<br>表示します。                                                                                 | 0                 | 0 | × | × |

| 16    | DMAエラーモニタ<br>(マスタアボート)   | DMAエラーコントロールレジスタのbit[16]をモニタ<br>表示します。                                                                                 | 0                 | 0 | × | × |

| 15:10 | 予約                       |                                                                                                                        | 000000            | 0 | X | × |

| 9     | テスト                      | 必ず"0"を書き込んでください。                                                                                                       | 0                 | 0 | 0 | × |

| 8     | IRQ#モニタ                  | IRQ#信号の状態をモニタします。                                                                                                      | X                 | 0 | X | X |

| 7:6   | 内部要因インタラプトリセット           | <ul><li>"1"を書くことによってbit[2:1]の内部要因インタラプトステータスを個別に"0"にクリアします。</li><li>bit7 : PCIクロックタイマ</li><li>bit6 : DMA転送終了</li></ul> | 00                | × | 0 | × |

| 5:4   | 内部要因インタラプト無効             | INTA#をアサートする2つの内部要因を個別に無効化します。"1"で無効になります。<br>bit5 : PCIクロックタイマ<br>bit4 : DMA転送終了                                      | 11                | 0 | 0 | × |

| 3     | 外部要因インタラプトマスク            | INTA#をアサートする外部要因であるIRQ#をマスクします。 "1"でマスクされます。                                                                           | 1                 | 0 | 0 | × |

| 2:1   | 内部要因インタラプト<br>ステータス      | INTA#をアサートする内部要因(PCIクロックタイマ・DMA転送終了)のステータスです。"1"が割り込み要因の発生を示します。<br>bit2: PCIクロックタイマ<br>bit1: DMA転送終了                  | 00                | 0 | × | × |

| 0     | 外部要因インタラプト<br>ステータス      | INTA#をアサートする外部要因(IRQ#)のステータスです。"1"が割り込み要因の発生を示します。本割り込みは ZEN7251G 上ではクリアできません。                                         | 0                 | 0 | × | × |

# 10.2.2.8. EEPROMコントロールレジスタ[Adr. 30h]

## 表37. EEPROMコントロールレジスタ

| ビット  | 名称                  | 機能                                              | リセット値                            | R | W | I |

|------|---------------------|-------------------------------------------------|----------------------------------|---|---|---|

| 31:8 | 予約                  |                                                 | 00000000<br>00000000<br>00000000 | 0 | × | × |

| 7:5  | 予約                  |                                                 | 000                              | 0 | × | X |

| 4    | EEPROM<br>イネーブル モニタ | このビットを通してEEN端子の値が読み出せます。                        | X                                | 0 | × | × |

| 3    | EEPROM<br>データアウト    | EEPROMへのデータ出力です。このビットに設定<br>した値がEDOより出力されます。    | О                                | 0 | 0 | × |

| 2    | EEPROM<br>データイン     | EEPROMからのデータ入力です。このビットを通してEDIの値が読み出せます。         | X                                | 0 | × | × |

| 1    | EEPROM<br>チップセレクト   | EEPROMのチップセレクト信号です。このビットに<br>設定した値がECSより出力されます。 | О                                | 0 | 0 | × |

| 0    | EEPROM クロック         | EEPROMのクロックです。このビットに設定した値がESKより出力されます。          | О                                | 0 | 0 | × |

## 10.2.2.9. デバイスコントロールレジスタ[Adr. 34h]

表38. デバイスコントロールレジスタ

| ビット   | 名称                  | 機能                                                                                                    | リセット値    | R | W       | Ι       |

|-------|---------------------|-------------------------------------------------------------------------------------------------------|----------|---|---------|---------|

| 31:24 | USERDEF             | ユーザ定義の領域です。                                                                                           | 00000000 | 0 | X       | $\circ$ |

| 23:8  | 予約                  |                                                                                                       | 00000000 | 0 | ×       | ×       |

| 7     | プリフェッチイネーブル         | "1"でメモリ領域へのターゲットリードアクセスの際、<br>プリフェッチを行います。                                                            | 0        | 0 | $\circ$ | 0       |

| 6:5   | プリフェッチ<br>データ設定     | メモリ領域のプリフェッチがbit[7]で許可されているとき、FIFOにどれだけのデータをプリフェッチするか選択します。 00:8データ 01:16データ 10:24データ 11:32データ        | 00       | 0 | 0       | 0       |

| 4     | プリフェッチ<br>転送トリガレベッレ | メモリ領域のプリフェッチがbit[7]で許可されているとき、FIFOにどれだけデータが書き込まれるとPCIのターゲットリードを受け付けるかを決めます。 0:1データ 1:プリフェッチデータ設定数の1/2 | 0        | 0 | 0       | 0       |

| 3     | WAIT#イネーブル          | "1"でWAIT#によるウェイトサイクルを有効にします。                                                                          | 0        | 0 | 0       | $\circ$ |

| 2     | ローカルリセット            | ローカルリセットを発生させます。"0"を書き込むとL<br>RST#が"0"となります。このビットは"1"が書き込ま<br>れるまでリセット状態を保持します。                       | 1        | 0 | 0       | ×       |

| 1     | PCIクロックタイマ<br>イネーブル | "1"でPCIクロックタイマがダウントを行います。                                                                             | 0        | 0 | 0       | ×       |

| 0     | PCIクロックタイマ<br>ロード   | "1"を書き込むとロードレジスタに設定されている値<br>をPCIクロックタイマにロードします。                                                      | 0        | × | 0       | ×       |

### 10.2.2.10. PCIクロックタイマロードレジスタ[Adr. 38h]

### 表39. PCIクロックタイマロードレジスタ

| ビット  | 名称                 | 機能                                                                                               | リセット値    | R | W | I |

|------|--------------------|--------------------------------------------------------------------------------------------------|----------|---|---|---|

| 31:0 | PCIクロックタイマ<br>ロード値 | PCIクロックタイマにロードする値を設定します。本<br>レジスタの値はデバイスコントロールレジスタの<br>bit[0]に"1"が書き込まれるとPCIクロックタイマに<br>ロードされます。 | 00000000 | 0 | 0 | × |

### 10.2.2.11. PCIクロックタイマレジスタ[Adr. 3ch]

## 表40. PCIクロックタイマレジスタ

| ビット  | 名称         | 機能                                                    | リセット値                            | R | W | Ι |

|------|------------|-------------------------------------------------------|----------------------------------|---|---|---|

| 31:0 | PCIクロックタイマ | 32bitの内蔵PCIクロックタイマです。本レジスタは<br>読取専用で直接値を書き込むことはできません。 | 00000000<br>00000000<br>00000000 | 0 | × | × |

## 10.2.2.12. DMA・転送コントロールレジスタ[Adr. 48h]

## 表41. DMA・転送コントロールレジスタ

| ビット   | 名称           | 機能                                                                                                                                                                                           | リセット値                        | R | W | Ι |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---|---|---|

| 31    | 転送イネーブル      | "1"を書くことによりDMA転送を開始します。転送<br>終了とともに"0"にクリアされます。また、"0"を書くこ<br>とにより強制終了することもできます。                                                                                                              | 0                            | 0 | 0 | × |

| 30:28 | PCI転送ドリガレベッレ | <ローカル to PCIの場合><br>FIFOにどれだけデータが格納されるとPCI側に転送を要求するかを決めます。<br><pci to="" ローカルの場合=""><br/>FIFOにどれだけ空きが存在するとPCI側に転送を要求するかを決めます。<br/>000:1<br/>001:8<br/>010:16<br/>011:24<br/>100~111:予約</pci> | 000                          | 0 | 0 | × |

| 27:26 | 転送セット有効設定    | <b>ZEN7251G</b> はDMA転送時のPCレバスのスタートアドレス及びデータ転送回数設定レジスタを4セット内蔵しています。この4セットのレジスタの内どこまで使用するかを決めます。 00: 1st→2nd 10: 1st→2nd→3rd 11: 1st→2nd→3rd→4th                                               | 00                           | 0 | 0 | × |

| 25    | ローカルバス転送領域   | "0"でメモリ領域、"1"でI/O領域に転送します。                                                                                                                                                                   | 0                            | 0 | 0 | × |

| 24    | 転送方向         | "0"でローカル to PCI、"1"でPCI to ローカルになります。                                                                                                                                                        | 0                            | 0 | 0 | × |

| 23:3  | 予約           |                                                                                                                                                                                              | 00000000<br>0000000<br>00000 | 0 | × | × |

| 2     | 強制終了処理モニタ    | "1"でDMAの強制終了処理中を示します。このbit<br>が"1"の間はDMAの強制終了処理中ですので、<br>新たなDMAの起動をしないようにして下さい。                                                                                                              | 0                            | 0 | × | × |

| 1:0   | 転送セットモニタ     | 現在、何番目の転送セットを実行中かモニタ表示します。転送終了時には最終の転送セットを表示したままになります。また、表示と転送セットの関係は次のようになります。<br>00:1st<br>01:2nd<br>10:3rd<br>11:4th                                                                      | 00                           | 0 | × | × |

# 10.2.2.13. DMA・エラーコントロールレジスタ[Adr. 4ch]

## 表42. DMA・エラーコントロールレジスタ

| ビット   | 名称                    | 機能                                                     | リセット値             | R | W | Ι |

|-------|-----------------------|--------------------------------------------------------|-------------------|---|---|---|

| 31:18 | 予約                    |                                                        | 0000000<br>000000 | 0 | × | X |

| 17    | エラー検出<br>(ターゲットアボート)  | DMA転送中にターゲットアボートを検出すると"1" になります。 "1"を書き込むと"0"にクリアされます。 | 0                 | 0 | 0 | × |