# ZEN1752F データシート

株式会社ジーニック

# Left blank

## 目次

| 1. 概要                                              | 1  |

|----------------------------------------------------|----|

| 2.特徵                                               | 1  |

| 3. ブロック図                                           | 2  |

| 4. 端子一覧                                            | 3  |

| 5. ホストインタフェース                                      | 4  |

| 5.1. ホストアクセス5.2. 割り込み                              |    |

| 6. 機能                                              | 5  |

| 6.1. 端子グループ<br>6.1.1. 端子グループ構成                     | 5  |

| 6.2. 汎用入出力                                         | 6  |

| 6.2.2.入出力方向選択                                      | 6  |

| 6.2.3.ポート割り込み<br>6.3. I 2 C マスタ                    | 7  |

| 6.3.1.I2 Cプロック構成                                   |    |

| 6.4.1. S PIブロック構成                                  |    |

| 6.4.3. 転送終了割り込み                                    | 8  |

| 6.4.4. セレクト信号アサート選択(オート/マニュアル)<br>6.4.5. bitオーダー選択 | 8  |

| 6.4.6.データの送受信タイミング選択<br>6.4.7.セレクト信号論理選択           |    |

| 6.4.8. S Piポートの切り替えについて                            |    |

| 6.5.1. UARTプロック構成                                  | 10 |

| 6.6. PWM                                           | 11 |

| 6.6.1. PWMブロック構成                                   |    |

| 6.6.3.送出回数選択<br>6.6.4.出力完了割り込み(非連続出力時のみ)           |    |

| 6.6.5.出力論理選択                                 | 11 |

|----------------------------------------------|----|

| 6.7. 赤外線リモコン                                 | 12 |

| 6.7.1. 赤外線リモコンブロック構成                         | 12 |

| 6.7.2. ワイズカウンタbit長                           | 12 |

| 6.7.3. 入力変化割り込み                              | 12 |

| 6.7.4.オーバーフロー検出割り込み                          | 12 |

| 6.7.5. ノイズフィルタ                               | 12 |

| 6.8. カウンタ                                    |    |

| 6.8.1.カウンタブロック構成                             | 13 |

| 6.8.2.カウンタモード                                | 14 |

| 6.8.3. Z相クリア                                 |    |

| 6.8.4.カウンタイネーブル                              |    |

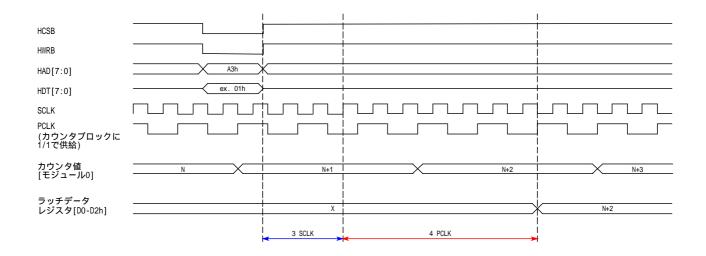

| 6.8.5. カウンタラッチ                               |    |

| 6.8.6. カウンタクリア                               |    |

| 6.8.7. <b>初期値ロード</b>                         |    |

| 6.8.8. 定周期自動ラッチ                              |    |

| 6.8.9. エッジ検出(パルス幅カウンタモード時のみ)                 |    |

| 6.8.10. オーバーフロー検出(パルス幅カウンタモード及び単相カウンタモード時のみ) |    |

| 6.8.11. 異常入力検出                               | 16 |

| 7. レジスター覧                                    | 17 |

| 7.1. アドレスマップ                                 | 17 |

| 8. レジスタ説明                                    | 22 |

| 8.1. システムリセットレジスタ[ A dr . 0 0 h ]            | 22 |

| 8.2. プロックリセットレジスタ0 [ A dr . 0 1 h ]          |    |

| 8.3. ブロックリセットレジスタ1 [ A dr . 0 2 h ]          |    |

| 8.4. クロックコントロールレジスタ0 [ Adr . 0 3 h ]         |    |

| 8.5. クロックコントロールレジスタ1 [ Adr . 0 4 h ]         |    |

| 8.6. クロックコントロールレジスタ2 [ A dr . 0 5 h ]        |    |

| 8.7. クロックコントロールレジスタ3 [ Adr. 06h]             |    |

| 8.8.クロックコントロー <b>ル</b> レジスタ4 [ Adr . 0 7 h ] |    |

| 8.9. クロックコントロールレジスタ5 [ Adr . 0 8 h ]         |    |

| 8.10. クロックコントロールレジスタ6 [ A dr . 0 9 h ]       | 29 |

| 8.11.クロックコントロールレジスタ7[Adr.0Ah]                | 30 |

| 8.12.クロックコントロールレジスタ8[Adr.0Bh]                | 31 |

| 8.13.クロックコントロールレジスタ9[Adr.0Ch]                |    |

| 8.1 4. 割り込みステータスレジスタ0 [ A dr . 0 D h ]       |    |

| 8.15.割り込みステータスレジスタ1[Adr.0Eh]                 |    |

| 8.1 6. 割り込みイネーブルレジスタ0 [Adr. 0 Fh]            |    |

| 8.17. 割り込みイネーブルレジスタ1 [Adr. 10h]              |    |

| 8.18.端子グループB機能選択レジスタ[Adr.11h]                | 27 |

| 8.19.端子グループC機能選択レジスタ[Adr.12h]                           | 38 |

|---------------------------------------------------------|----|

| 8.2 0. ブロックスタンバイレジスタ0 [ Adr . 1 3 h ]                   |    |

| 8.2 1. ブロックスタンバイレジスタ1 [ Adr . 1 4 h ]                   |    |

| 8.2 2. ポートアサインレジスタ[Adr. 15h]                            | 41 |

| 8.23. UART <b>ループバ</b> ックレジスタ[Adr. 16h]                 | 41 |

| 8.24.ポートA方向設定レジスタ[Adr.20h]                              |    |

| 8.25. ポートAデータレジスタ[Adr. 21h]                             | 42 |

| 8.26.ポートA割り込みステータスレジスタ[Adr.22h]                         | 42 |

| 8.27.ポートA割り込みイネーブルレジスタ[Adr.23h]                         | 43 |

| 8.28.ポートA割り込みエッジ選択レジスタ[Adr.24h]                         | 43 |

| 8.29.ポートB方向設定レジスタL[Adr.25h]                             | 44 |

| 8.30.ポートB方向設定レジスタH[Adr.26h]                             | 44 |

| 8.3 1. ポートBデータレジスタL [ A dr . 2 7 h ]                    | 44 |

| 8.32.ポートBデータレジスタH[Adr.28h]                              | 45 |

| 8.33.ポートC方向設定レジスタL[Adr.29h]                             | 45 |

| 8.34.ポートC方向設定レジスタH[Adr.2Ah]                             | 45 |

| 8.35. ポートCデータレジスタL[Adr.2Bh]                             | 46 |

| 8.3 6. ポートC データレジスタH [ A dr . 2 C h ]                   | 46 |

| 8.37.ポートD方向設定レジスタL[Adr.2Dh]                             | 46 |

| 8.38.ポートD方向設定レジスタH[Adr.2Eh]                             |    |

| 8.39. ポートDデータレジスタL[Adr. 2Fh]                            |    |

| 8.40.ポートDデータレジスタH[Adr.30h]                              | 47 |

| 8.4 1. [2 C プリスケールレジスタL [ A dr . 4 0 h ]                | 48 |

| 8.42.I2CプリスケールレジスタH[Adr.41h]                            |    |

| 8.43.I2C割り込みイネーブルレジスタ[Adr.42h]                          |    |

| 8.4 4. [2 C割り込みステータスレジスタ[Adr. 43h]                      | 49 |

| 8.45.[2C送信データレジスタ[Adr.44h]                              |    |

| 8.46.12C受信データレジスタ[Adr.45h]                              |    |

| 8.47.[2Cコマンドレジスタ[Adr.46h]                               | 50 |

| 8.48.12Cステータスレジスタ[Adr.47h]                              |    |

| 8.49. S PIコントロールレジスタ[Adr.50h]                           |    |

| 8.50. S P.転送スタートレジスタ[Adr.51h]                           |    |

| 8.5 1. S P <b>i転送</b> bit <b>長レジスタ</b> [ A dr . 5 2 h ] |    |

| 8.5 2. S Pi割り込みステータスレジスタ[ A dr . 5 3 h]                 |    |

| 8.5 3. S Pi割り込みイネーブルレジスタ[ A dr . 5 4 h ]                |    |

| 8.5 4. S PI出力データレジスタ0 [ A dr . 5 5 h ]                  |    |

| 8.5 5. S PI出力データレジスタ1 [ A dr . 5 6 h ]                  |    |

| 8.5 6. S PI出力データレジスタ2 [ A dr . 5 7 h ]                  |    |

| 8.5 7. S PI出力データレジスタ3 [ A dr . 5 8 h ]                  |    |

| 8.5 8. S PI入力データレジスタ0 [ A dr . 5 9 h ]                  |    |

| 8.5 9. S PI入力データレジスタ1 [ A dr . 5 A h ]                  |    |

| 8.60. S PI入力データレジスタ2 [ A dr . 5 B h ]                   | 54 |

| 8.6 1. S PI入力データレジスタ3 [ A dr . 5 C h ]               | 54 |

|------------------------------------------------------|----|

| 8.62. S PIセレクト信号アサート制御レジスタ[Adr.5Dh]                  | 55 |

| 8.63. UART設定レジスタ0(RBR/THR/DLL)[Adr. 60h、68h、70h、78h] | 56 |

| 8.64. UART設定レジスタ1(IER/DLM)[Adr. 61h、69h、71h、79h]     | 57 |

| 8.65. UART設定レジスタ2 (!!R / FCR) [Adr. 62h、6Ah、72h、7Ah] | 58 |

| 8.66. UART設定レジスタ3(LCR)[Adr. 63h、6Bh、73h、7Bh]         | 60 |

| 8.67. UART設定レジスタ4(MCR)[Adr. 64h、6Ch、74h、7Ch]         |    |

| 8.68.UART設定レジスタ5(LSR)[Adr.65h、6Dh、75h、7Dh]           | 62 |

| 8.69. UART設定レジスタ6 (MSR) [Adr. 66h、6Eh、76h、7Eh]       | 63 |

| 8.70.UART設定レジスタ7(SCR)[Adr.67h、6Fh、77h、7Fh]           | 63 |

| 8.7 1. PWMコントロールレジスタ[Adr. 80h]                       | 64 |

| 8.7 2. PWM割り込みステータスレジスタ[Adr.81h]                     | 65 |

| 8.7 3. PWM割り込みイネーブルレジスタ[Adr. 82h]                    |    |

| 8.7 4. PWM出力デューティ設定レジスタ0 [ A dr . 8 4 h ]            | 66 |

| 8.75. PWM出力デューティ設定レジスタ1 [ A dr . 85 h ]              | 66 |

| 8.7 6. PWM出力デューティ設定レジスタ2 [ A dr . 8 6 h ]            |    |

| 8.77. PWM出力回数設定レジスタ0[Adr.88h]                        | 67 |

| 8.78.PWM出力回数設定レジスタ1[Adr.89h]                         | 67 |

| 8.79. PWM出力回数設定レジスタ2[Adr.8Ah]                        |    |

| 8.80. 赤外線リモコンコントロールレジスタ[Adr.90h]                     | 68 |

| 8.81. 赤外線リモコンノイズフィルタレジスタ[Adr.91h]                    |    |

| 8.82.赤外線リモコン割り込みステータスレジスタ[Adr.92h]                   |    |

| 8.83. 赤外線リモコン割り込みイネーブルレジスタ[Adr.93h]                  |    |

| 8.84. 赤外線リモコンHighワイズカウンタL[Adr.94h]                   |    |

| 8.85. 赤外線リモコンHighワイズカウンタH[Adr.95h]                   |    |

| 8.86.赤外線リモコンLowワイズカウンタL[Adr.96h]                     |    |

| 8.87. 赤外線リモコンLowワイズカウンタH[Adr.97h]                    | 71 |

| 8.88.カウンタモードレジスタ0[Adr.A0h]                           |    |

| 8.89.カウンタモードレジスタ1[Adr. A1h]                          |    |

| 8.90.カウンタイネーブルレジスタ[Adr.A2h]                          |    |

| 8.9 1. カウンタラッチコマンドレジスタ[Adr. A3h]                     |    |

| 8.9 2. カウンタクリアコマンドレジスタ[Adr. A4h]                     |    |

| 8.93.カウンタロードコマンドレジスタ[Adr.A5h]                        |    |

| 8.9 4. カウンタZ相イネーブルレジスタ[Adr. A6h]                     |    |

| 8.95.カウンタ定周期自動ラッチイネーブルレジスタ[Adr.A7h]                  |    |

| 8.9 6. カウンタ割り込みイネーブルレジスタ0 [ Adr . A 8 h ]            |    |

| 8.97.カウンタ割り込みイネーブルレジスタ1[Adr. A9h]                    |    |

| 8.98.カウンタ割り込みイネーブルレジスタ2[Adr. AAh]                    |    |

| 8.9 9. カウンタ割り込みイネーブルレジスタ3 [ A dr . A B h ]           |    |

| 8.100.カウンタ周期レジスタ0L[Adr.B0h]                          |    |

| 8.101.カウンタ周期レジスタ0H[Adr.B1h]                          |    |

| 8.10.2.カウンタ周期レジスタ1 I [ Adr. B 2 h ]                  | 85 |

| 8.103.カウンタ周期レジスタ1H[Adr.B3h]          | 86  |

|--------------------------------------|-----|

| 8.104.カウンタ周期レジスタ2L[Adr.B4h]          | 86  |

| 8.105.カウンタ周期レジスタ2H[Adr.B5h]          |     |

| 8.106.カウンタ周期レジスタ3L[Adr.B6h]          |     |

| 8.107. <b>カウンタ周期レジス</b> タ3H[Adr.B7h] |     |

| 8.108.カウンタ割り込みステータスレジスタ0[Adr.B8h]    |     |

| 8.109.カウンタ割り込みステータスレジスタ1[Adr.B9h]    |     |

| 8.110.カウンタ割り込みステータスレジスタ2[Adr.BAh]    |     |

| 8.111.カウンタ割り込みステータスレジスタ3[Adr.BBh]    |     |

| 8.112.カウンタロードデータレジスタ00[Adr.C0h]      | 92  |

| 8.113.カウンタロードデータレジスタ01[Adr.C1h]      |     |

| 8.114.カウンタロードデータレジスタ02[Adr.C2h]      |     |

| 8.115.カウンタロードデータレジスタ10[Adr.C4h]      |     |

| 8.116.カウンタロードデータレジスタ11[Adr. C5h]     | 93  |

| 8.117.カウンタロードデータレジスタ12[Adr.C6h]      | 93  |

| 8.118.カウンタロードデータレジスタ20[Adr.C8h]      | 94  |

| 8.119.カウンタロードデータレジスタ21[Adr.C9h]      | 94  |

| 8.120.カウンタロードデータレジスタ22[Adr.CAh]      | 94  |

| 8.121.カウンタロードデータレジスタ30[Adr.CCh]      | 95  |

| 8.122.カウンタロードデータレジスタ31[Adr.CDh]      |     |

| 8.123.カウンタロードデータレジスタ32[Adr.CEh]      | 95  |

| 8.124.カウンタラッチデータレジスタ00[Adr.D0h]      | 96  |

| 8.125.カウンタラッチデータレジスタ01[Adr.D1h]      |     |

| 8.126.カウンタラッチデータレジスタ02[Adr.D2h]      | 96  |

| 8.127.カウンタラッチデータレジスタ10[Adr.D4h]      |     |

| 8.128.カウンタラッチデータレジスタ11[Adr.D5h]      | 97  |

| 8.129.カウンタラッチデータレジスタ12[Adr.D6h]      | 97  |

| 8.130.カウンタラッチデータレジスタ20[Adr.D8h]      | 98  |

| 8.131.カウンタラッチデータレジスタ21[Adr.D9h]      | 98  |

| 8.132.カウンタラッチデータレジスタ22[Adr.DAh]      | 98  |

| 8.133.カウンタラッチデータレジスタ30[Adr.DCh]      |     |

| 8.134.カウンタラッチデータレジスタ31[Adr.DDh]      | 99  |

| 8.135. カウンタラッチデータレジスタ32[Adr. DEh]    |     |

| 9. 電気的特性                             | 100 |

|                                      |     |

| 9.1. 絶対最大定格<br>9.2. 推奨動作条件           | 100 |

| 9.3. 直流特性                            |     |

| 9.4. 交流特性                            |     |

| 9.5. タイミングダイアグラム                     |     |

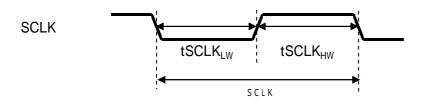

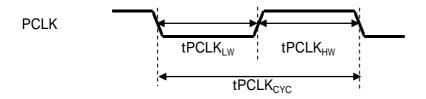

| 9.5.1. クロック                          |     |

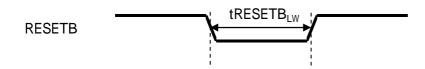

| 9.5.2. リセット                          |     |

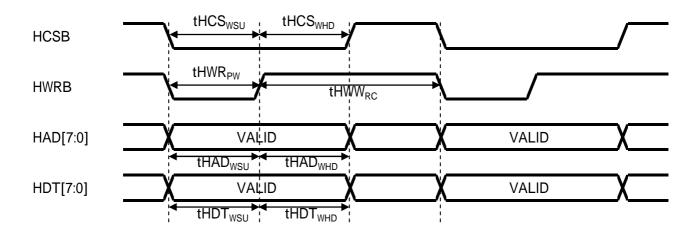

|     | 9.5.3. ホストインタフェース      | 105 |

|-----|------------------------|-----|

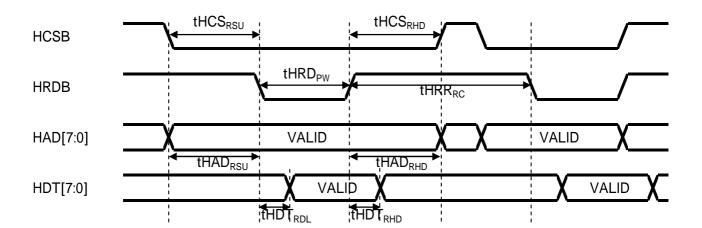

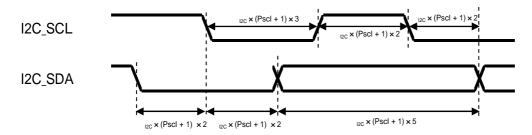

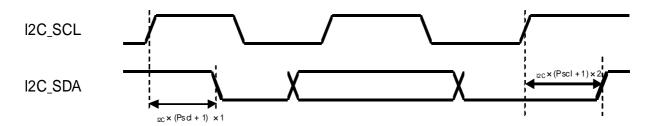

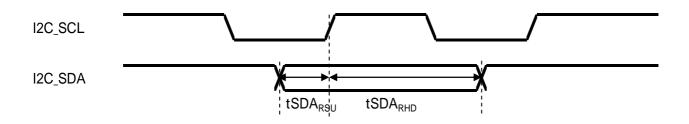

|     | 9.5.4.[2 <b>Cア</b> クセス | 106 |

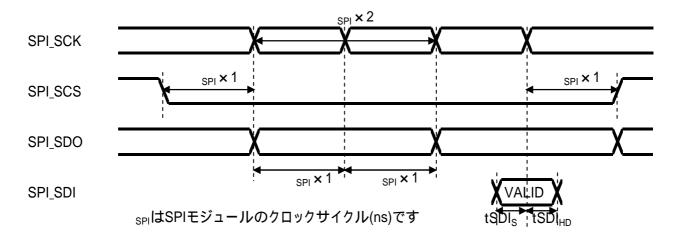

|     | 9.5.5. S PIアクセス        | 108 |

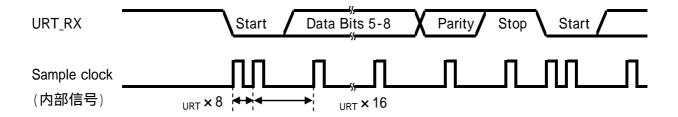

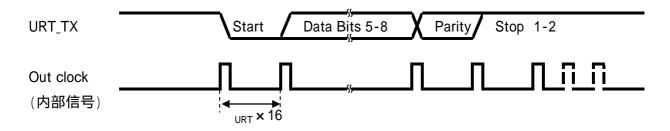

|     | 9.5.6. UART            | 108 |

|     | 9.5.7. PWM             |     |

|     | 9.5.8. 赤外線リモコン         | 109 |

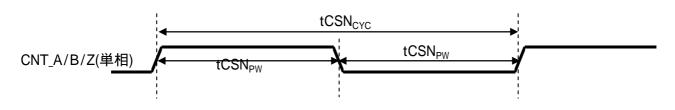

|     | 9.5.9. カウンタ            | 110 |

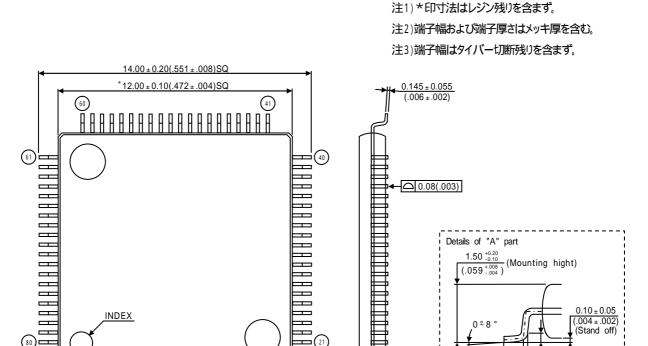

| 1 0 | ). パッケージ形状             | 111 |

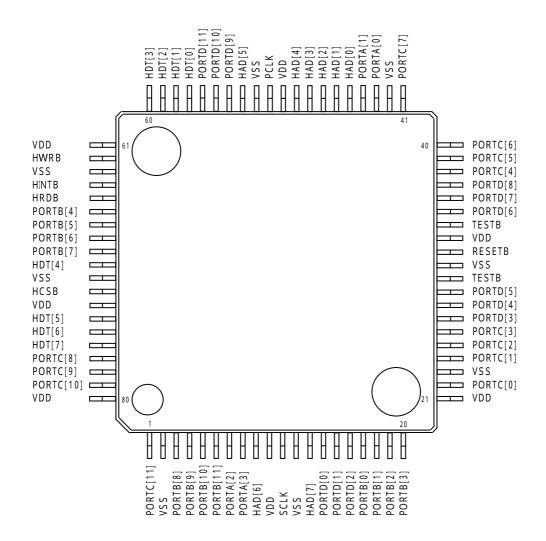

| 11  | . 端子配置                 | 112 |

| 1 2 | . 改訂履歴                 | 113 |

### 1. 概要

ZEN1752Fは、映像機器やFA機器等で利用頻度の高い機能を1チップにまとめたマイコン周辺拡張LSIです。 搭載している機能は、汎用入出力、パCマスタ、SPI、PWM出力、赤外線リモコン入力、UART及びパルスカウンタです。 各ブロックを個別にスタンバイ・モードに移行させることが可能であるため、低消費電力システムを実現することができます。 各ペリフェラルの多様な動作レート要求に柔軟に対応するため、各ブロックは2種類のクロックソースから動作クロックを選択することができます(ただし、汎用入出力及びUARTはSCLK専用)。

PC はフィリップス社の商標です。なお、本ドキュメントでは以降I2Cと表記します。

## 2. 特徵

CPU I/F : 8 bitパラレルインタフェース

汎用入出力 : Max40本(うち36本が他の信号と兼用)

ポートA: 専用ポート4本(1本毎に入出力/割り込み設定が可能)

ポートB : 兼用ポート12本(1本毎に入出力設定が可能) ポートC : 兼用ポート12本(1本毎に入出力設定が可能) ポートD : 兼用ポート12本(1本毎に入出力設定が可能)

出力電流容量 : Io = ± 4mA

スタンバイ・モード: ブロックごとに動作クロックを停止可能I2 C マスタ: Max6ch(切り替えて使用)[SPIと端子共有]S PI(4線式シリアル): Max3ch(切り替えて使用)[I2 Cと端子共有]

UART : Max4ch(独立) PWM : Max3ch(独立)

パルス幅精度

: 8 bit

赤外線リモコン入力

: Max1ch

パルス幅精度

: 16 bit

パルスカウンタ : Max12ch(単相カウンタモード)、Max4ch(2相カウンタモード/パルス幅カウンタモード) カウント精度 : 8 bit(単相カウンタモード)、24bit(2相カウンタモード)、12bit(パルス幅カウンタモード)

パルス幅カウンタモード: High / Lowのパルス幅をカウント

単相カウンタモード:アップ信号

2相カウンタモード : A B相 / アップ・ダウン信号

システムクロック : Max50MHz

ペリフェラルクロック : Max25MHz(ただし、ペリフェラルクロックの周波数 システムクロックの周波数/2)

電源電圧 : 3.3 V 単一(全入力5 V トレラント)

パッケージ: LQFP80ピン(12×12mm、0.5mmピッチ)

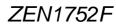

## 3. ブロック図

図1.ブロック図

## 4. 端子一覧

表1.端子一覧表

| ピン番号                                        | 記号          | 信号名                 | 属性      | 機能                                  |

|---------------------------------------------|-------------|---------------------|---------|-------------------------------------|

| 11                                          | SCLK        | System Clock        | IN      | システムクロック                            |

| 51                                          | PCLK        | Peripheral Clock    | IN      | ペリフェラルクロック                          |

| 32                                          | RESETB      | System Reset        | IN 1    | システムリセット                            |

| 72                                          | HCSB        | Host<br>Chip Select | IN      | チップセレクト                             |

| 6 2                                         | HWRB        | Host Write          | IN      | ライトストローブ                            |

| 6.5                                         | HRDB        | Host Read           | IN      | リードストローブ                            |

| 13,9,53,<br>49~45                           | HAD[7:0]    | Host<br>Address Bus | IN      | アドレスバス                              |

| 76~74,70,<br>60~57                          | HDT[7:0]    | Host<br>Data Bus    | INOUT 1 | データバス                               |

| 6 4                                         | HINTB       | Host Int Output     | OUT     | 割り込み出力                              |

| 8 ~ 7 ,<br>4 4 ~ 4 3                        | PORTA[3:0]  | Port A              | INOUT 1 | 端子グループA(汎用入出力)                      |

| 6 ~ 3,<br>69 ~ 66,<br>20 ~ 17               | PORTB[11:0] | Port B              | INOUT 1 | 端子グループB(汎用入出力、PWM/IRRC/<br>UARTを選択) |

| 1,79~77,<br>41~38,<br>26~24,<br>22          | PORTC[11:0] | Port C              | INOUT 1 | 端子グループC(汎用入出力、I2C、SPIを選択)           |

| 56 ~ 54,<br>37 ~ 35,<br>29 ~ 27,<br>16 ~ 14 | PORTD[11:0] | Port D              | INOUT 1 | 端子グループD(汎用入出力、カウンタを選択)              |

| 34,30                                       | TESTB       | Test                | IN      | テスト用端子 VDDレベルに固定してください              |

| 73,33,<br>80,61,50,<br>21,10                | VDD         | Power               | -       | 電源(+3.3V)                           |

| 63,52,42,<br>23,12,2,<br>71,31              | VSS         | Ground              | -       | グランド(0V)                            |

<sup>1</sup> これらの入力バッファはシュミットトリガです。

## 5. ホストインタフェース

## 5.1. ホストアクセス

ホストから ZEN1752F へのアクセスは、HCSB、HWRB、HRDB、HAD[7:0]およびHDT[7:0]により ZEN1752F のレジスタにアクセスします。

表2.ホストアクセス

| アクセス | HCSB | HWRB | HRDB | HAD[7:0] | HDT[7:0] |

|------|------|------|------|----------|----------|

| 書き込み | 0    | 0    | 1    | アドレス     | 書き込みデータ  |

| 読み出し | 0    | 1    | 0    | アドレス     | 読み出しデータ  |

| NOP  | 1    | Χ    | X    | Χ        | Hi - Z   |

| 禁止   | 0    | 0    | 0    | X        | 不定       |

### 5.2. 割り込み

ZEN1752Fの各ブロック/モジュールからの割り込み要求をHINTB端子から出力します。 割り込みの解除は、各ブロック/モジュールの割り込み要因をクリアすることにより、解除されます。

HINTBは、Lowアクティブです。

- 1:割り込み要求なし

- 0:割り込み要求あり

## 6. 機能

## 6.1. 端子グループ

#### 6.1.1. 端子グループ構成

ZEN1752F はグループA ~ グループDまで4つの端子グループがあり、各端子グループによって割り当てることができる機能が異なります。

各端子グループの初期状態(リセット後)はHi - Zになっていますので、リセット期間も含めてリセット後から端子グループの機能を設定するまでの期間は主意が必要です。必要に応じて、端子を抵抗でプルアップまたはプルダウンしてください。

表3.端子グループ別機能構成

| 端子グループ | 端子名       | 1/0 | 選択機能  | 端子記号    | 1/0 | 選択機能   | 端子記号   | 1/0 |

|--------|-----------|-----|-------|---------|-----|--------|--------|-----|

|        | PORTA[3]  | 1/0 |       |         |     |        |        |     |

| グループA  | PORTA[2]  | 1/0 | -     | -       | -   | -      | -      | -   |

| 77V 7A | PORTA[1]  | 1/0 |       |         |     |        |        |     |

|        | PORTA[0]  | 1/0 |       |         |     |        |        |     |

|        | PORTB[11] | 1/0 | UART3 | URT3RX  | I   |        |        |     |

|        | PORTB[10] | 1/0 | UARTS | URT3TX  | 0   |        |        |     |

|        | PORTB[9]  | 1/0 | UART2 | URT2RX  | I   |        |        |     |

|        | PORTB[8]  | 1/0 | UARTZ | URT2TX  | 0   |        |        |     |

|        | PORTB[7]  | 1/0 | UART1 | URT1RX  | I   |        |        |     |

| グループB  | PORTB[6]  | 1/0 | UARTI | URT1TX  | 0   | -      | -      | -   |

| 770 75 | PORTB[5]  | 1/0 | UART0 | URT0RX  | I   |        |        |     |

|        | PORTB[4]  | 1/0 | UARTU | URT0TX  | 0   |        |        |     |

|        | PORTB[3]  | 1/0 | IRRC  | IRRC    | I   |        |        |     |

|        | PORTB[2]  | 1/0 | PWM2  | PWM2    | 0   |        |        |     |

|        | PORTB[1]  | 1/0 | PWM1  | PWM1    | 0   |        |        |     |

|        | PORTB[0]  | 1/0 | PWM0  | PWM0    | 0   |        |        |     |

|        | PORTC[11] | 1/0 |       | SPI_SCS | 0   | I2 C 5 | I2CSDA | 1/0 |

|        | PORTC[10] | 1/0 | SPI2  | SPI_SDO | 0   | I2C3   | I2CSCL | 0   |

|        | PORTC[9]  | 1/0 | 3112  | SPI_SDI | I   |        | I2CSDA | 1/0 |

|        | PORTC[8]  | 1/0 |       | SPI_SCK | 0   |        | I2CSCL | 0   |

|        | PORTC[7]  | 1/0 |       | SPI_SCS | 0   | 12.02  | I2CSDA | 1/0 |

| グループC  | PORTC[6]  | 1/0 | SPI1  | SPI_SDO | 0   | I2 C 3 | I2CSCL | 0   |

| 770 70 | PORTC[5]  | 1/0 | 2111  | SPI_SDI | I   | I2 C 2 | I2CSDA | 1/0 |

|        | PORTC[4]  | 1/0 |       | SPI_SCK | 0   | 12 C 2 | I2CSCL | 0   |

|        | PORTC[3]  | 1/0 |       | SPI_SCS | 0   | I2 C 1 | I2CSDA | 1/0 |

|        | PORTC[2]  | 1/0 | SPI0  | SPI_SDO | 0   | 12 C 1 | I2CSCL | 0   |

|        | PORTC[1]  | 1/0 | 3110  | SPI_SDI | I   | I2 C 0 | I2CSDA | 1/0 |

|        | PORTC[0]  | 1/0 |       | SPI_SCK | 0   | 12 C U | I2CSCL | 0   |

|        | PORTD[11] | 1/0 |       | CNT3_Z  | I   |        |        |     |

|        | PORTD[10] | I/0 | CNT3  | CNT3_B  | I   |        |        |     |

|        | PORTD[9]  | I/0 |       | CNT3A   | I   |        |        |     |

|        | PORTD[8]  | I/0 |       | CNT2_Z  | I   |        |        |     |

|        | PORTD[7]  | I/0 | CNT2  | CNT2_B  | I   |        |        |     |

| グループD  | PORTD[6]  | 1/0 |       | CNT2A   | I   | -      | -      | -   |

| 770 70 | PORTD[5]  | 1/0 |       | CNT1_Z  | I   |        |        |     |

|        | PORTD[4]  | 1/0 | CNT1  | CNT1_B  | I   |        |        |     |

|        | PORTD[3]  | 1/0 |       | CNT1_A  | I   |        |        |     |

|        | PORTD[2]  | 1/0 |       | CNT0_Z  | I   |        |        |     |

|        | PORTD[1]  | 1/0 | CNT0  | CNT0_B  | I   |        |        |     |

|        | PORTD[0]  | 1/0 |       | CNT0_A  | I   |        |        |     |

### 6.2. 汎用入出力

#### 6.2.1. 汎用入出力モジュール

ZEN1752F はポートA~ポートDまで4つの汎用入出力モジュールを内蔵しており、それぞれが端子グループA~端子グループDに割り当てられています。

なお、ポートAの4本につきましては割り込み入力として使用することも可能です。

#### 表4.汎用入出力モジュール

| 汎用入出力モジュール信号名 | 入出力 | 信 <del>号</del> 数 | 備考                    |

|---------------|-----|------------------|-----------------------|

| PORTA         | 入出力 | 4本               | 割り込み機能あり              |

| PORTB         | 入出力 | 12本              | PWM、IRRC、UARTと汎用入出力兼用 |

| PORTC         | 入出力 | 12本              | I2C、SPIと汎用入出力兼用       |

| PORTD         | 入出力 | 12本              | CNTと汎用入出力兼用           |

#### 6.2.2. 入出力方向選択

機能選択により汎用入出力モジュールになっている端子の入出力方向をbit単位で設定することができます。

#### 6.2.3. ポート割り込み

ポートAの端子が変化(立ち上がり、立ち下がり)すること(割り込み要因)により割り込み要求を発生させることができます。 割り込み要求はbit単位で有効/無効を設定することができ、割り込み要因である端子の変化の方向もbit単位で設定することが可能です。

ポートAのみの機能です。

## 6.3. I2 Cマスタ

#### 6.3.1. [2 C ブロック構成

ZEN1752F は12 C ブロック内に1つの12 C マスタモジュールを内蔵し、6組の12 C マスタポートを有しています。各12 C マスタポートは同時には使用することはできません。レジスタ設定によって1ポートのみ有効になります。

マルチマスタバスとしては機能しませんので(アービトレーション不可、クロック同期認識不可)、他のマスタデバイスは接続できません。

表5.12Cモジュール機能信号構成

| I2Cモジュール信号名 | 入出力 | 信 <del>号</del> 数 | 備考         |

|-------------|-----|------------------|------------|

| I2C_SCL     | 出力  | 1本               | I2Cバス クロック |

| I2CSDA      | 入出力 | 1本               | I2Cバス データ  |

#### 6.4. S PIマスタ

#### 6.4.1. S PIブロック構成

ZEN1752F はS PIブロック内に1つのS PIマスタモジュールを内蔵し、3組のS PIマスタポートを有しています。各S PIマスタポートは同時には使用することはできません。レジスタ設定によって1ポートのみ有効になります。

表6.SPIモジュール機能信号構成

| SPIモジュール信号名 | 入出力 | 信 <del>号</del> 数 | 備考              |

|-------------|-----|------------------|-----------------|

| SPI_SCK     | 出力  | 1本               | SPI シリアル転送クロック  |

| SPI_SDI     | 入力  | 1本               | SPI シリアル転送入力データ |

| SPI_SDO     | 出力  | 1本               | SPI シリアル転送出力データ |

| SPI_SCS     | 出力  | 1本               | SPI シリアル転送セレクト  |

#### 6.4.2. 転送データ長

最長32bitまでの転送が一度に可能です。

#### 6.4.3. 転送終了割り込み

1回の転送が終了した際に割り込み要求を発生させることができます。

#### 6.4.4. セレクト信号アサート選択(オート/マニュアル)

有効になっているSPIポートのSPI\_SCS信号を転送中自動的にアサートするか、レジスタによるマニュアルコントロールにするかを選択できます。

#### 6.4.5. bitオーダー選択

シリアルデータの送受信に関して、MSBとLSBのどちらから先に出力するかを選択できます。

#### 6.4.6. データの送受信タイミング選択

SPIシリアル転送クロックの立ち上がりまたは立ち下がりに同期して、データの送受信を行うことができます。 タイミングは送信 / 受信個別に選択可能です。

#### 6.4.7. セレクト信号論理選択

SPI SCS信号の論理を正/負選択可能です。

#### 6.4.8. SPIポートの切り替えについて

端子グループ機能選択レジスタにおいてSPIブロックが選択されている状態で、ポートアサインレジスタ(15h)のSPIPASにより選択されていないSPI端子出力は、Hi - Z状態になります。SPIのセレクト信号(SPI\_\_SCS)の極性が異なるデバイス間で切替を行う場合、いったんポートアサインレジスタ(15h)に30hを書き込み、全SPIポートをHi - Z状態にすることにより、ポート切り替え時に意図せずSPIデバイスをアクティブ状態にすることが避けられます。ただし、SPIの端子は、接続するデバイスの仕様を考慮し適切にプルアップまたはプルダウンしてください。

#### 6.5. **UART**

### 6.5.1. UARTブロック構成

ZEN1752FはUARTブロック内に4つのUARTモジュールを内蔵しています。 各UARTモジュールは、SCLKのみで動作します。PCLKでは動作しません。

#### 表7.UARTモジュール機能信号構成

| UARTモジュール信号名 | 入出力 | 信 <del>号</del> 数 | 備考         |

|--------------|-----|------------------|------------|

| URTTX        | 出力  | 1本               | UART 送信データ |

| URTRX        | 入力  | 1本               | UART 受信データ |

#### 6.5.2. ループバック接続

各モジュール単体でのループバックとは別に、2つのUARTモジュール(0と1の接続:URT0\_\_TX URT1\_\_RX、URT1\_\_TX URT0\_\_RX、2と3の接続:URT2\_\_TX URT3\_\_RX、URT3\_\_TX URT2\_\_RX)を ZEN1752F 内でループバック接続することができます。

#### 6.6. PWM

#### 6.6.1. PWMブロック構成

ZEN1752F はPWMブロック内に3つのPWMモジュールを内蔵しています。 各PWMモジュールは、独立したクロックで動作します。

#### 表8. PWMモジュール機能信号構成

| PWMモジュール信号名 | 入出力 | 信 <del>号</del> 数 | 備考           |

|-------------|-----|------------------|--------------|

| PWM         | 出力  | 1本               | PWM パルス出力データ |

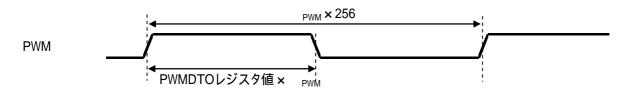

#### 6.6.2. PWM分解能

PWMのパルス周期の分解能は8bitです。デューティ設定は動作中に変更可能です。

#### 6.6.3. 送出回数選択

設定されたデューティ比のパルスを何回(PWMパルス周期回)送出するかを設定できます。 設定範囲は1~255及び連続です。

#### 6.6.4. 出力完了割り込み(非連続出力時のみ)

出力が完了したタイミングで割り込み要求を発生させることが可能です。

#### 6.6.5. 出力論理選択

PWM信号の出力論理を選択できます。

### 6.7. 赤外線リモコン

#### 6.7.1. 赤外線リモコンブロック構成

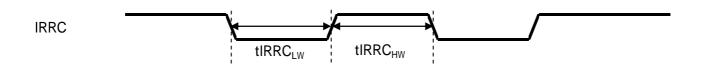

ZEN1752F は赤外線リモコンブロック内に1つの赤外線リモコン受信モジュールを内蔵しています。このモジュールはプリスケーラ、High / Lowワイズカウンタ及びノイズフィルタから構成されます。

#### 表9.赤外線リモコンモジュール機能信号構成

| 赤外線リモコンモジュール信号名 | 入出力 | 信 <del>号</del> 数 | 備考           |

|-----------------|-----|------------------|--------------|

| IRRC            | 入力  | 1本               | IRリモコン 入力データ |

#### 6.7.2. ワイズカウンタbit長

Highワイズ、Lowワイズとも16bitのカウンタで入力信号のパルス幅をカウント可能です。

#### 6.7.3. 入力変化割り込み

赤外線リモコン信号の入力変化ごとに割り込み要求を発生させることができます(ただし、有効な値がカウンタに格納されていない場合には自動的に割り込み要求をマスクします)。割り込み要因として、端子の立ち上がり/立ち下がり検出を独立して設定可能です。

#### 6.7.4. オーバーフロー検出割り込み

ワイズカウンタがオーバーフローした場合に割り込みを出すことができます。Highワイズ / Lowワイズ独立して設定可能です。なお、オーバーフローした場合ワイズカウンタの値はOhで保持されます。

#### 6.7.5. ノイズフィルタ

赤外線リモコン信号のノイズを除去します。設定数以下のクロック幅のパルスは無視されます。Highパルス / Lowパルス独立して設定可能です。

## 6.8. カウンタ

#### 6.8.1. カウンタブロック構成

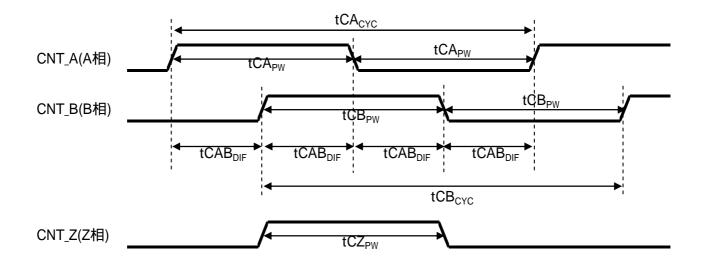

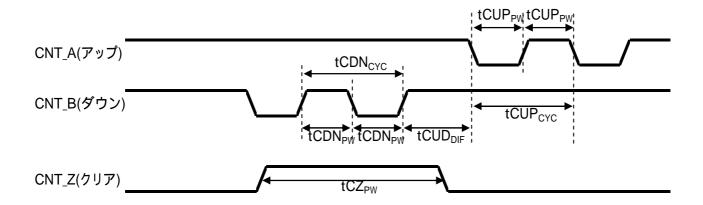

ZEN1752F はカウンタブロック内に4つのカウンタモジュールを内蔵し、各モジュールはさらに3つの8bitのカウンタユニットから構成されます。単相カウンタモード時には各ユニットが独立して有効になり8bitのアップカウンタ3ch.、2相カウンタモード時には3ユニットまとめて24bitのアップダウンカウンタ1ch.、パルス幅カウンタモード時は3ユニットまとめて12bitのLowパルス幅及び12bitのHighパルス幅カウンタ1ch.として利用できます。

表 10. カウンタモジュール機能信号構成

| CNTモジュール信<br>号名 | 入出力 | 信号数 | 単相カウンタ<br>モード | 2相カウンタ<br>モード | パルス幅カウンタ<br>モード |

|-----------------|-----|-----|---------------|---------------|-----------------|

| CNTA            | 入力  | 1本  | アップパルス        | A相パルス / アップパ  | カウント対象信号(Low    |

|                 |     |     |               | ルス            | /High幅)         |

| CNT_B           | 入力  | 1本  | アップパルス        | B相パルス / ダウンパ  | 未使用(汎用入出力と      |

|                 |     |     |               | ルス            | して使用可)          |

| CNT_Z           | 入力  | 1本  | アップパルス        | Z相パルス/クリアパル   | 未使用(汎用入出力と      |

|                 |     |     |               | ス             | して使用可)          |

#### 表 11. カウンタ構成

| カウンタモジュール        | カウンタユニット   | 単相カウンタ<br>モード | 2相カウンタ<br>モード         | パルス幅カウンタ<br>モード                |

|------------------|------------|---------------|-----------------------|--------------------------------|

|                  | カウンタユニット00 | ch.0          | ch.0(下位byte)          | ch.0(Low <b>パル</b> ス幅[7:0])    |

| <br>  カウンタモジュール0 | カウンタユニット01 | ch.1          | ch.0(中位byte)          | ch.0(High <b>パリレス幅</b> [7:0])  |

| 13727 624 700    | カウンタユニット02 | ch.2          | ch.0( <b>上位</b> byte) | ch.0(High <b>パルス幅</b> [11:8]+  |

|                  |            |               |                       | Lowパルス幅[11:8])                 |

|                  | カウンタユニット10 | ch.3          | ch.1(下位byte)          | ch.1(Low <b>パル</b> ス幅[7:0])    |

| <br>  カウンタモジュール1 | カウンタユニット11 | ch.4          | ch.1(中位byte)          | ch.1(High <b>パリレス幅</b> [7:0])  |

| カランタモシュール        | カウンタユニット12 | ch.5          | ch.1( <b>上位</b> byte) | ch.1(High <b>パリレス幅</b> [11:8]+ |

|                  |            |               |                       | Lowパルス幅[11:8])                 |

|                  | カウンタユニット20 | ch.6          | ch.2(下位byte)          | ch.2(Low <b>パル</b> ス幅[7:0])    |

| <br>  カウンタモジュール2 | カウンタユニット21 | ch.7          | ch.2(中位byte)          | ch.2(High <b>パリレス幅</b> [7:0])  |

| 11777 671-102    | カウンタユニット22 | ch.8          | ch.2( <b>上位</b> byte) | ch.2(High <b>パリレス幅</b> [11:8]+ |

|                  |            |               |                       | Lowパルス幅[11:8])                 |

|                  | カウンタユニット30 | ch.9          | ch.3(下位byte)          | ch.3(Low <b>パル</b> ス幅[7:0])    |

| <br>  カウンタモジュール3 | カウンタユニット31 | ch.10         | ch.3(中位byte)          | ch.3(High <b>パリレス幅</b> [7:0])  |

| リングみエシュール3       | カウンタユニット32 | ch.11         | ch.3( <b>上位</b> byte) | ch.3(High <b>パリレ</b> ス幅[11:8]+ |

|                  |            |               |                       | Lowパルス幅[11:8])                 |

#### 6.8.2. カウンタモード

ZEN1752F は下表のようなカウンタモードに対応しています。

表 12. カウンタモード

| カウンタモード | パルス入力形式      | カウント逓倍 | Z相クリア | カウンタ動作                               |

|---------|--------------|--------|-------|--------------------------------------|

| 単相      | アップパルス       | -      | なし    | CNT_A(B、Z)入力の立ち上がリエッジで<br>カウントします。   |

|         | アップダウンパルス    | -      | あり    | CNT_A入力及びCNT_B入力の立ち上がリエッジでカウントします。   |

| 2相      | A / B相パルス    | 1逓倍    | あり    | CNT_A入力のエッジ変化(CNT_B入力がL時のみ)でカウントします。 |

|         | A / DIA/ OVA | 4逓倍    | あり    | CNT_A入力及びCNT_B入力のエッジ<br>変化でカウントします。  |

| パルス幅    | カウント対象信号     | -      | -     | CNT_AのLow幅およびHigh幅をカウントします。          |

#### 6.8.3. Z相クリア

2相カウンタモードに設定されているカウンタモジュールはCNT\_Z入力の立ち上がリエッジで当該カウンタをクリアできます。 本機能は有効/無効を設定できます。

#### 6.8.4. カウンタイネーブル

カウント動作を停止 / 起動することができます。このイネーブル動作はカウンタモジュールごとに個別に可能ですが、単相カウンタモードに設定されている場合、1つのモジュール内の3ch.の単相カウンタは同時に停止 / 起動されます。なお、カウント動作の停止 / 起動にかかわらず、カウンタラッチ、カウンタクリア及び初期値ロードは常に可能です。

#### 6.8.5. カウンタラッチ

カウンタ値を24bit一括してラッチレジスタに格納できます。読み出し中にカウンタ値が変動するのを防ぐため、まずラッチコマンドを実行しカウンタ値をラッチデータレジスタに取り込んでから読み取ります。このラッチ動作はカウンタモジュールごとに個別に可能ですが、単相カウンタモードに設定されている場合、1つのモジュール内の3ch.の単相カウンタは同時にラッチされます。なお、定周期自動ラッチ及びパルス幅カウンタモード時は所定のタイミングで自動的にラッチされますので、読み出しの際に事前にカウンタラッチコマンドを実行する必要はありません。

#### 6.8.6. カウンタクリア

カウンタ値をクリアすることができます。このクリア動作はカウンタモジュールごとに個別に可能ですが、単相カウンタモードに設定されている場合、1つのモジュール内の3ch.の単相カウンタは同時に0hにクリアされます。また、パルス幅カウンタモードの場合、Highパルス幅カウンタ及びLowパルス幅カウンタの両方とも同時にクリアされます。

なお、定周期自動ラッチ機能がイネーブルになっている場合は、カウンタと共に定周期用カウンタも同時にクリアします。この機能により、最初の周期におけるカウンタ値から正確な値を取得することが可能になります。

#### 6.8.7. 初期値ロード

事前にロードデータレジスタに書き込んでおいた24bitの初期値を一括してカウンタにロードできます。このロード動作はカウンタモジュールごとに個別に可能ですが、単相カウンタモードに設定されている場合、1つのモジュール内の3ch.の単相カウンタは同時に初期値ロードされます。なお、パルス幅カウンタモード時も、同時に3つのユニットにロードされますのでご注意ください。

#### 6.8.8. 定周期自動ラッチ

各カウンタモジュールについて、あらかじめ設定した周期ごとに入力されたパルスの数をカウンタ値として読み出すことができます。この周期はカウンタ周期設定レジスタによって設定されたクロック数(256~16776960:256の倍数)で決定されます。この周期毎にカウンタ値をラッチレジスタに格納します。このときカウンタはリセットされ、その後自動的にカウントを再開します。リセット時にアップ(またはダウン)しなければならない場合、カウンタ値は1h(またはFFh[単相カウンタモード]、FFFFFFh[2相カウンタモード])にセットされます。また、本設定が有効などき、カウンタ値がラッチレジスタに格納される毎に割り込み要求を発生させることも可能です。

#### 6.8.9. エッジ検出(パルス幅カウンタモード時のみ)

パルス幅カウンタモードに設定されているカウンタモジュールについては、立ち上がり及び立ち下がりエッジの入力を検出した場合に割り込み要求を発生させることが可能です(立ち上がりと立ち下がりは個別に設定できます)。なお、このエッジ検出動作はカウンタモジュールが停止状態のときも有効です。

#### 6.8.10. オーバーフロー検出(パルス幅カウンタモード及び単相カウンタモード時のみ)

単相カウンタモードに設定されているカウンタモジュールについては、いずれかのカウンタユニットのカウンタ値がオーバーフローした場合に割り込み要求を発生させることが可能です。ただし、割り込み要求の有効/無効はカウンタモジュールごとの設定となります(カウンタユニットごとに独立した設定はできません)。なお、カウンタ値がオーバーフローした場合、単相カウンタモード時はカウント動作は継続し、パルス幅カウンタモード時は0hが保持されます(ただし、次の立ち上がりないし立ち下がりエッジが入力されるとカウント動作を再開します)。

#### 6.8.11. 異常入力検出

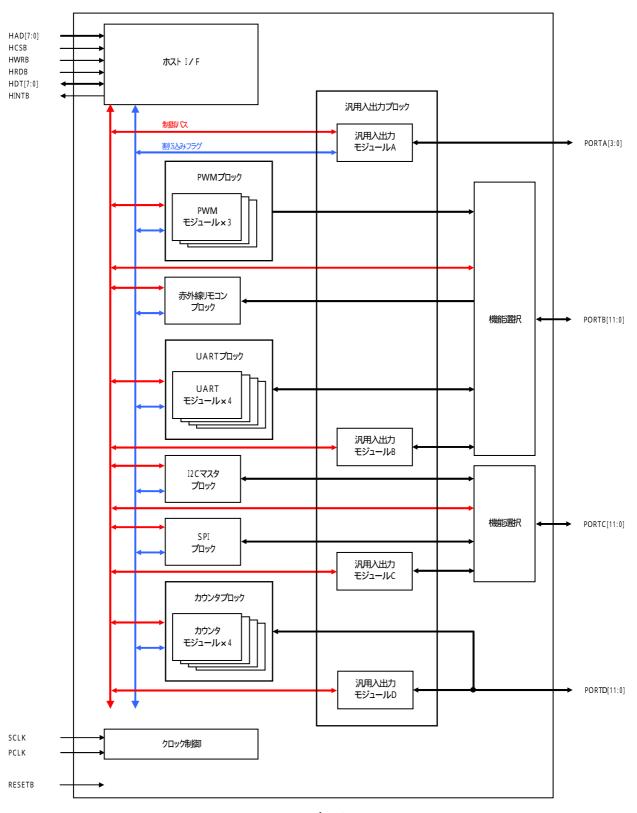

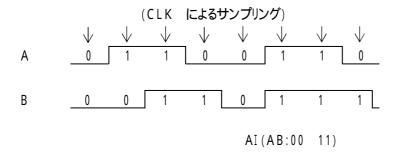

ZEN1752F はAB相入力が正常な位相遷移状態を行っているかどうかを検出する機能を有しています。この機能は2相力ウンタモード(AB相入力)のときのみ有効です。また異常入力検出時には、カウンタ値の信頼性は失われます。例えば、下図で示すような異常な遷移状態が起こると異常入力ステータスレジスタの値が"1"となり異常入力(AI)フラグが発生します。この異常な遷移状態の原因には次のようなことが考えられます。

- (1) A B相入力 A、Bの周波数が、システムクロック周波数の1 / 4を超えたために、 正確に位相遷移状態をクロックでサンプリングできなくなった場合

- (2) ラインノイズが混入し、入力パルス変化として観測され異常な遷移状態と判断した場合

図2. A B相入力の異常検出例

図3.AB相入力の状態遷移例

## 7. レジスタ一覧

## 7.1. アドレスマップ

表13~17に ZEN1752F のアドレスマッピングを示します。各レジスタの詳細は8章を参照してください。

表 13.アドレスマッピング(その1)

| アドレス(h) | 名称                | リセット値 | R/W |

|---------|-------------------|-------|-----|

| 0 0     | システムリセットレジスタ      | 0 0 h | R/W |

| 0 1     | ブロックリセットレジスタ0     | 0 0 h | R/W |

| 02      | ブロックリセットレジスタ1     | 0 0 h | R/W |

| 03      | クロックコントロールレジスタ0   | 0 0 h | R/W |

| 0 4     | クロックコントロールレジスタ1   | 0 0 h | R/W |

| 05      | クロックコントロールレジスタ2   | 0 0 h | R/W |

| 0 6     | クロックコントロールレジスタ3   | 0 0 h | R/W |

| 07      | クロックコントロールレジスタ4   | 00h   | R/W |

| 0 8     | クロックコントロールレジスタ5   | 00h   | R/W |

| 0 9     | クロックコントロールレジスタ6   | 00h   | R/W |

| 0 A     | クロックコントロールレジスタ7   | 00h   | R/W |

| 0 B     | クロックコントロールレジスタ8   | 00h   | R/W |

| 0 C     | クロックコントロールレジスタ9   | 00h   | R/W |

| 0 D     | 割り込みステータスレジスタ0    | 0 0 h | R   |

| 0 E     | 割り込みステータスレジスタ1    | 00h   | R   |

| 0 F     | 割り込みイネーブルレジスタロ    | 0 0 h | R/W |

| 10      | 割り込みイネーブルレジスタ1    | 00h   | R/W |

| 11      | 端子グループB端子機能選択レジスタ | 00h   | R/W |

| 12      | 端子グループC端子機能選択レジスタ | 00h   | R/W |

| 13      | ブロックスタンバイレジスタ0    | 00h   | R/W |

| 1 4     | ブロックスタンバイレジスタ1    | 00h   | R/W |

| 15      | ポートアサインレジスタ       | 30h   | R/W |

| 16      | UARTJレープバックレジスタ   | 00h   | R/W |

| 17 ~ 1F | 予約                | -     | 1   |

## 表 14.アドレスマッピング(その2)

| アドレス(h)   | 名称                   | リセット値 | R/W |

|-----------|----------------------|-------|-----|

| 20        | ポートA方向設定レジスタ         | 0 F h | R/W |

| 21        | ポートAデータレジスタ          | 00h   | R/W |

| 22        | ポートA割り込みステータスレジスタ    | 00h   | R/W |

| 23        | ポートA割り込みイネーブルレジスタ    | 00h   | R/W |

| 2 4       | ポートA割り込みエッジ選択レジスタ    | 00h   | R/W |

| 25        | ポートB方向設定レジスタL        | FFh   | R/W |

| 26        | ポートB方向設定レジスタH        | 0 F h | R/W |

| 27        | ポートBデータレジスタL         | 00h   | R/W |

| 28        | ポートBデータレジスタH         | 00h   | R/W |

| 29        | ポートC方向設定レジスタL        | FFh   | R/W |

| 2 A       | ポートC方向設定レジスタH        | 0 F h | R/W |

| 2 B       | ポートC データレジスタL        | 00h   | R/W |

| 2 C       | ポートC データレジスタH        | 00h   | R/W |

| 2 D       | ポートD方向設定レジスタL        | FFh   | R/W |

| 2 E       | ポートD方向設定レジスタH        | 0 F h | R/W |

| 2 F       | ポートDデータレジスタL         | 00h   | R/W |

| 30        | ポートDデータレジスタH         | 00h   | R/W |

| 31 ~ 3F   | 予約                   | -     | -   |

| 4 0       | I2CプリスケールレジスタL       | 01h   | R/W |

| 41        | I2CプリスケールレジスタH       | 00h   | R/W |

| 42        | 12 C割り込みイネーブルレジスタ    | 00h   | R/W |

| 43        | 12 C割り込みステータスレジスタ    | 00h   | R/W |

| 4 4       | I2C送信データレジスタ         | 00h   | R/W |

| 45        | I2C受信データレジスタ         | 00h   | R   |

| 46        | I2Cコマンドレジスタ          | 00h   | R/W |

| 47        | I2Cステータスレジスタ         | 00h   | R   |

| 48 ~ 4F   | 予約                   | -     | -   |

| 5 0       | SPIコントロールレジスタ        | 00h   | R/W |

| 51        | SPI転送スタートレジスタ        | 00h   | R/W |

| 52        | SPI転送bit長レジスタ        | 00h   | R/W |

| 53        | SPI割り込みステータスレジスタ     | 00h   | R/W |

| 5 4       | SPI割り込みイネーブルレジスタ     | 00h   | R/W |

| 5 5       | SPI出力データレジスタ0[7:0]   | 00h   | R/W |

| 5 6       | SPI出力データレジスタ1[15:8]  | 00h   | R/W |

| 57        | SPI出力データレジスタ2[23:16] | 00h   | R/W |

| 5 8       | SPI出力データレジスタ3[31:24] | 00h   | R/W |

| 5 9       | SPI入力データレジスタ0[7:0]   | 00h   | R   |

| 5 A       | SPI入力データレジスタ1[15:8]  | 00h   | R   |

| 5 B       | SPI入力データレジスタ2[23:16] | 00h   | R   |

| 5 C       | SPI入力データレジスタ3[31:24] | 00h   | R   |

| 5 D       | SPIセレクト信号アサート制御レジスタ  | 00h   | R/W |

| 5 E ~ 5 F | 予約                   | -     | -   |

## 表 15.アドレスマッピング(その3)

| アドレス(h) | 名称                          | リセット値 | R/W |

|---------|-----------------------------|-------|-----|

| 6 0     | UART設定レジスタO(for UARTモジュールO) | 00h   | R/W |

| 61      | UART設定レジスタ1(for UARTモジュール0) | 0 0 h | R/W |

| 62      | UART設定レジスタ2(for UARTモジュール0) | 00h   | R/W |

| 63      | UART設定レジスタ3(for UARTモジュール0) | 0 0 h | R/W |

| 6 4     | UART設定レジスタ4(for UARTモジュール0) | 00h   | R/W |

| 65      | UART設定レジスタ5(for UARTモジュール0) | 60h   | R/W |

| 66      | UART設定レジスタ6(for UARTモジュール0) | FBh   | R/W |

| 67      | UART設定レジスタ7(for UARTモジュール0) | 00h   | R/W |

| 68      | UART設定レジスタO(for UARTモジュール1) | 00h   | R/W |

| 6 9     | UART設定レジスタ1(for UARTモジュール1) | 00h   | R/W |

| 6 A     | UART設定レジスタ2(for UARTモジュール1) | 00h   | R/W |

| 6 B     | UART設定レジスタ3(for UARTモジュール1) | 00h   | R/W |

| 6 C     | UART設定レジスタ4(for UARTモジュール1) | 00h   | R/W |

| 6 D     | UART設定レジスタ5(for UARTモジュール1) | 60h   | R/W |

| 6 E     | UART設定レジスタ6(for UARTモジュール1) | FBh   | R/W |

| 6 F     | UART設定レジスタ7(for UARTモジュール1) | 00h   | R/W |

| 7 0     | UART設定レジスタO(for UARTモジュール2) | 00h   | R/W |

| 71      | UART設定レジスタ1(for UARTモジュール2) | 00h   | R/W |

| 7 2     | UART設定レジスタ2(for UARTモジュール2) | 00h   | R/W |

| 73      | UART設定レジスタ3(for UARTモジュール2) | 00h   | R/W |

| 7 4     | UART設定レジスタ4(for UARTモジュール2) | 00h   | R/W |

| 75      | UART設定レジスタ5(for UARTモジュール2) | 60h   | R/W |

| 7 6     | UART設定レジスタ6(for UARTモジュール2) | FBh   | R/W |

| 77      | UART設定レジスタ7(for UARTモジュール2) | 00h   | R/W |

| 7.8     | UART設定レジスタ0(for UARTモジュール3) | 00h   | R/W |

| 7 9     | UART設定レジスタ1(for UARTモジュール3) | 00h   | R/W |

| 7 A     | UART設定レジスタ2(for UARTモジュール3) | 00h   | R/W |

| 7 B     | UART設定レジスタ3(for UARTモジュール3) | 00h   | R/W |

| 7 C     | UART設定レジスタ4(for UARTモジュール3) | 00h   | R/W |

| 7 D     | UART設定レジスタ5(for UARTモジュール3) | 60h   | R/W |

| 7 E     | UART設定レジスタ6(for UARTモジュール3) | FBh   | R/W |

| 7 F     | UART設定レジスタ7(for UARTモジュール3) | 00h   | R/W |

| 8 0     | PWMコントロールレジスタ               | 00h   | R/W |

| 8 1     | PWM割り込みステータスレジスタ            | 00h   | R/W |

| 8 2     | PWM割り込みイネーブルレジスタ            | 00h   | R/W |

| 83      | 予約                          | -     | -   |

| 8 4     | PWM出力デューティ設定レジスタ0           | 00h   | R/W |

| 8 5     | PWM出力デューティ設定レジスタ1           | 00h   | R/W |

| 8 6     | PWM出力デューティ設定レジスタ2           | 00h   | R/W |

| 87      | 予約                          | -     | -   |

| 88      | PWM出力回数設定レジスタ0              | 00h   | R/W |

| 8 9     | PWM出力回数設定レジスタ1              | 00h   | R/W |

| 8 A     | PWM出力回数設定レジスタ2              | 00h   | R/W |

| 8B~8F   | 予約                          | -     | -   |

## 表 16.アドレスマッピング(その4)

| アドレス(h)    | 名称                    | リセット値 | R/W |

|------------|-----------------------|-------|-----|

| 9 0        | 赤外線リモコンコントロールレジスタ     | 0 0 h | R/W |

| 91         | 赤外線リモコンノイズフィルタレジスタ    | 0 0 h | R/W |

| 9 2        | 赤外線リモコン割り込みステータスレジスタ  | 0 0 h | R/W |

| 93         | 赤外線リモコン割り込みイネーブルレジスタ  | 0 0 h | R/W |

| 9 4        | 赤外線リモコンHighワイズカウンタL   | 0 0 h | R   |

| 95         | 赤外線リモコンHighワイズカウンタH   | 0 0 h | R   |

| 9 6        | 赤外線リモコンLowワイズカウンタL    | 0 0 h | R   |

| 9 7        | 赤外線リモコンLowワイズカウンタ_H   | 0 0 h | R   |

| 98~9F      | 予約                    | -     | -   |

| A 0        | カウンタモードレジスタ0          | 0 0 h | R/W |

| A 1        | カウンタモードレジスタ1          | 0 0 h | R/W |

| A 2        | カウンタイネーブルレジスタ         | 00h   | R/W |

| A 3        | カウンタラッチコマンドレジスタ       | 0 0 h | R/W |

| A 4        | カウンタクリアコマンドレジスタ       | 00h   | R/W |

| A 5        | カウンタロードコマンドレジスタ       | 0 0 h | R/W |

| A 6        | カウンタZ相イネーブルレジスタ       | 00h   | R/W |

| A 7        | カウンタ定周期自動ラッチイネーブルレジスタ | 00h   | R/W |

| A 8        | カウンタ割り込みイネーブルレジスタ0    | 00h   | R/W |

| A 9        | カウンタ割り込みイネーブルレジスタ1    | 0 0 h | R/W |

| AA         | カウンタ割り込みイネーブルレジスタ2    | 00h   | R/W |

| A B        | カウンタ割り込みイネーブルレジスタ3    | 0 0 h | R/W |

| A C ~ A F  | 予約                    | -     | -   |

| B 0        | カウンタ周期間設定レジスタ0_L      | 01h   | R/W |

| B1         | カウンタ周期設定レジスタ0_H       | 0 0 h | R/W |

| B 2        | カウンタ周期設定レジスタ1_L       | 01h   | R/W |

| В3         | カウンタ周期設定レジスタ1_H       | 0 0 h | R/W |

| B 4        | カウンタ周期設定レジスタ2_L       | 01h   | R/W |

| B 5        | カウンタ周期設定レジスタ2_H       | 0 0 h | R/W |

| B 6        | カウンタ周期設定レジスタ3_L       | 01h   | R/W |

| В7         | カウンタ周期設定レジスタ3_H       | 0 0 h | R/W |

| B 8        | カウンタ割り込みステータスレジスタ0    | 0 0 h | R/W |

| B 9        | カウンタ割り込みステータスレジスタ1    | 00h   | R/W |

| ВА         | カウンタ割り込みステータスレジスタ2    | 00h   | R/W |

| ВВ         | カウンタ割り込みステータスレジスタ3    | 00h   | R/W |

| BC~BF      | 予約                    | -     | -   |

| C 0        | カウンタロードデータレジスタ00      | 00h   | R/W |

| C 1        | カウンタロードデータレジスタ01      | 0 0 h | R/W |

| C 2        | カウンタロードデータレジスタ02      | 0 0 h | R/W |

| C 3        | 予約                    | -     | -   |

| C 4        | カウンタロードデータレジスタ10      | 00h   | R/W |

| C 5        | カウンタロードデータレジスタ11      | 00h   | R/W |

| C 6        | カウンタロードデータレジスタ12      | 0 0 h | R/W |

| <b>C</b> 7 | 予約                    | -     | -   |

## 表 17.アドレスマッピング(その5)

| アドレス(h)   | 名称               | リセット値 | R/W |

|-----------|------------------|-------|-----|

| C 8       | カウンタロードデータレジスタ20 | 00h   | R/W |

| C 9       | カウンタロードデータレジスタ21 | 00h   | R/W |

| CA        | カウンタロードデータレジスタ22 | 00h   | R/W |

| CB        | 予約               | -     | 1   |

| CC        | カウンタロードデータレジスタ30 | 00h   | R/W |

| CD        | カウンタロードデータレジスタ31 | 00h   | R/W |

| CE        | カウンタロードデータレジスタ32 | 00h   | R/W |

| CF        | 予約               | -     | I   |

| D 0       | カウンタラッチデータレジスタ00 | 00h   | R   |

| D1        | カウンタラッチデータレジスタ01 | 00h   | R   |

| D 2       | カウンタラッチデータレジスタ02 | 00h   | R   |

| D3        | 予約               | -     | 1   |

| D 4       | カウンタラッチデータレジスタ10 | 00h   | R   |

| D 5       | カウンタラッチデータレジスタ11 | 00h   | R   |

| D 6       | カウンタラッチデータレジスタ12 | 00h   | R   |

| D7        | 予約               | -     | 1   |

| D 8       | カウンタラッチデータレジスタ20 | 00h   | R   |

| D 9       | カウンタラッチデータレジスタ21 | 00h   | R   |

| DA        | カウンタラッチデータレジスタ22 | 00h   | R   |

| DB        | 予約               | -     | 1   |

| DC        | カウンタラッチデータレジスタ30 | 00h   | R   |

| DD        | カウンタラッチデータレジスタ31 | 00h   | R   |

| DE        | カウンタラッチデータレジスタ32 | 00h   | R   |

| DF        | 予約               | -     | •   |

| E 0 ~ F F | 予約               | -     | -   |

## 8. レジスタ説明

## 8.1. システムリセットレジスタ[Adr.00h]

本レジスタ以外の全レジスタ値が、リセット値に初期化されます。 自動では"0"に復帰しません。

表 18.システムリセットレジスタ

| I | bit | 名称     | 機能                                 | リセット値  | R | W |

|---|-----|--------|------------------------------------|--------|---|---|

|   | 7:1 | 予約     |                                    | 000000 |   | × |

|   | 0   | SRESET | 全レジスタ値の初期化を行います。<br>1:リセット<br>0:通常 | 0      |   |   |

## 8.2. ブロックリセットレジスタ0[Adr.01h]

各ファンクションブロック及びモジュールをリセットします(当該ブロック及びモジュールに関連するレジスタもリセットされます)。なお、SPIRESではペリフェラルポートセレクトレジスタ[Adr.15h]のbit[5:4]もリセットされますのでご注意ください。 自動では"0"に復帰しません。

表 19. ブロックリセットレジスタ0

| bit | 名称      | 機能                                     | リセット値 | R | W |

|-----|---------|----------------------------------------|-------|---|---|

| 7   | URT3RES | UARTモジュール3の初期化を行います。<br>1:リセット<br>0:通常 | 0     |   |   |

| 6   | URT2RES | UARTモジュール2の初期化を行います。<br>1:リセット<br>0:通常 | 0     |   |   |

| 5   | URT1RES | UARTモジュール1の初期化を行います。<br>1:リセット<br>0:通常 | 0     |   |   |

| 4   | URT0RES | UARTモジュール0の初期化を行います。<br>1:リセット<br>0:通常 | 0     |   |   |

| 3:2 | 予約      |                                        | 0 0   |   | × |

| 1   | SPIRES  | S P I ブロックの初期化を行います。<br>1:リセット<br>0:通常 | 0     |   |   |

| 0   | I2 CRES | I2Cプロックの初期化を行います。<br>1:リセット<br>0:通常    | 0     |   |   |

## 8.3. ブロックリセットレジスタ1[Adr.02h]

各ファンクションブロック及びモジュールをリセットします(当該ブロック及びモジュールに関連するレジスタもリセットされます)。

自動では"0"に復帰しません。

## 表20.ブロックリセットレジスタ1

| bit | 名称      | 機能                    | リセット値 | R | W |

|-----|---------|-----------------------|-------|---|---|

|     |         | カウンタモジュール3の初期化を行います。  |       |   |   |

| 7   | CNT3RES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | カウンタモジュール2の初期化を行います。  |       |   |   |

| 6   | CNT2RES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | カウンタモジュール1の初期化を行います。  |       |   |   |

| 5   | CNT1RES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | カウンタモジュール0の初期化を行います。  |       |   |   |

| 4   | CNTORES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | 赤外線リモコンブロックの初期化を行います。 |       |   |   |

| 3   | IRRCRES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | PWMモジュール2の初期化を行います。   |       |   |   |

| 2   | PWM2RES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | PWMモジュール1の初期化を行います。   |       |   |   |

| 1   | PWM1RES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

|     |         | PWMモジュール0の初期化を行います。   |       |   |   |

| 0   | PWM0RES | 1:リセット                | 0     |   |   |

|     |         | 0:通常                  |       |   |   |

## 8.4. クロックコントロールレジスタ0[Adr.03h]

I2Cブロックのクロックを選択します。I2Cブロックの転送レートを調整するための分周設定はI2Cプリスケールレジスタ[Adr. 40h/41h]で決定します。

表 21.クロックコントロールレジスタ0

| bit | 名称        | 機能                                          | リセット値   | R | W |

|-----|-----------|---------------------------------------------|---------|---|---|

| 7   | I2CCLKSEL | I2Cプロックに供給するクロックを選択します。<br>1:PCLK<br>0:SCLK | 0       |   |   |

| 6:0 | 予約        |                                             | 0000000 |   | × |

## 8.5. クロックコントロールレジスタ1 [Adr. 04h]

SPIブロックのクロックの設定を行います。

表22.クロックコントロールレジスタ1

| bit | 名称        | 機能                                                                                                     | リセット値 | R | W |

|-----|-----------|--------------------------------------------------------------------------------------------------------|-------|---|---|

| 7   | SPICLKSEL | SPIモジュールのクロックの原振を選択します。<br>1:PCLK<br>0:SCLK                                                            | 0     |   |   |

| 6:3 | 予約        |                                                                                                        | 0000  |   | × |

| 2:0 | SPICLKDIV | SPIモジュールに供給するクロックの分周設定をします。 111:1/128 110:1/64 101:1/32 100:1/16 011:1/8 010:1/4 001:1/2 000:スルー(分周なし) | 000   |   |   |

## 8.6. クロックコントロールレジスタ2[Adr.05h]

PWMモジュール0のクロックの設定を行います。

#### 表23.クロックコントロールレジスタ2

| bit | 名称         | 機能                                                                                                                                                                                                         | リセット値 | R | W |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|---|

| 7   | PWM0CLKSEL | PWMモジュール0の原振を選択します。<br>1:PCLK<br>0:SCLK                                                                                                                                                                    | 0     |   |   |

| 6:4 | 予約         |                                                                                                                                                                                                            | 000   |   | × |

| 3:0 | PWM0CLKDIV | PWMモジュール0に供給するクロックの分周設定をします。 1111:予約 1110:1/16384 1101:1/8192 1100:1/4096 1011:1/2048 1010:1/1024 1001:1/512 1000:1/256 0111:1/128 0110:1/64 0101:1/32 0100:1/16 0011:1/8 0010:1/4 0001:1/2 0000:スルー(分周なし) | 0000  |   |   |

## 8.7. クロックコントロールレジスタ3[Adr.06h]

PWMモジュール1のクロックの設定を行います。

#### 表24.クロックコントロールレジスタ3

| bit | 名称          | 機能                                                                                                                                                                                                         | リセット値 | R | W |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|---|

| 7   | PWM1CLKSEL  | PWMモジュール1の原振を選択します。<br>1:PCLK<br>0:SCLK                                                                                                                                                                    | 0     |   |   |

| 6:4 | 予約          |                                                                                                                                                                                                            | 000   |   | × |

| 3:0 | PWM1CLK DIV | PWMモジュール1に供給するクロックの分周設定をします。 1111:予約 1110:1/16384 1101:1/8192 1100:1/4096 1011:1/2048 1010:1/1024 1001:1/512 1000:1/256 0111:1/128 0110:1/64 0101:1/32 0100:1/16 0011:1/8 0010:1/4 0001:1/2 0000:スルー(分周なし) | 0000  |   |   |

## 8.8. クロックコントロールレジスタ4[Adr.07h]

PWMモジュール2のクロックの設定を行います。

#### 表25.クロックコントロールレジスタ4

| bit | 名称         | 機能                                                                                                                                                                                                         | リセット値 | R | W |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|---|

| 7   | PWM2CLKSEL | PWMモジュール2の原振を選択します。<br>1:PCLK<br>0:SCLK                                                                                                                                                                    | 0     |   |   |

| 6:4 | 予約         |                                                                                                                                                                                                            | 000   |   | × |

| 3:0 | PWM2CLKDIV | PWMモジュール2に供給するクロックの分周設定をします。 1111:予約 1110:1/16384 1101:1/8192 1100:1/4096 1011:1/2048 1010:1/1024 1001:1/512 1000:1/256 0111:1/128 0110:1/64 0101:1/32 0100:1/16 0011:1/8 0010:1/4 0001:1/2 0000:スルー(分周なし) | 0000  |   |   |

## 8.9. クロックコントロールレジスタ5 [Adr. 08h]

赤外線リモコンブロックのクロックの設定を行います。

#### 表26.クロックコントロールレジスタ5

| bit | 名称         | 機能                                                                                                        | リセット値 | R | W |

|-----|------------|-----------------------------------------------------------------------------------------------------------|-------|---|---|

| 7   | IRRCCLKSEL | 赤外線リモコンブロックの原振を選択します。<br>1:PCLK<br>0:SCLK                                                                 | 0     |   |   |

| 6:3 | 予約         |                                                                                                           | 0000  |   | × |

| 2:0 | IRRCCLKDIV | 赤外線リモコンブロックに供給するクロックの分周設定をします。 111:1/128 110:1/64 101:1/32 100:1/16 011:1/8 010:1/4 001:1/2 000:スルー(分周なし) | 000   |   |   |

# 8.10. クロックコントロールレジスタ6[Adr.09h]

カウンタモジュール0のクロックの設定を行います。

### 表27.クロックコントロールレジスタ6

| bit | 名称         | 機能                                       | リセット値 | R | W |

|-----|------------|------------------------------------------|-------|---|---|

| 7   | CNT0CLKSEL | カウンタモジュール0の原振を選択します。<br>1:PCLK<br>0:SCLK | 0     |   |   |

| 6:4 | 予約         |                                          | 000   |   | × |

| 3:0 | CNTOCLKDIV | カウンタモジュール0に供給するクロックの分周設定をします。            | 0000  |   |   |

# 8.11. クロックコントロー**ル**レジスタ7[Adr.0Ah]

カウンタモジュール1のクロックの設定を行います。

# 表28.クロックコントロールレジスタ7

| bit | 名称         | 機能                                                                                                                                                                                                                                | リセット値 | R | W |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|---|

| 7   | CNT1CLKSEL | カウンタモジュール1の原振を選択します。<br>1:PCLK<br>0:SCLK                                                                                                                                                                                          | 0     |   |   |

| 6:4 | 予約         |                                                                                                                                                                                                                                   | 000   |   | × |

| 3:0 | CNT1CLKDIV | カウンタモジュール1に供給するクロックの分周設定をします。     1100~1111:設定禁止     1011:1/2048     1010:1/1024     1001:1/512     1000:1/256     0111:1/128     0110:1/64     0101:1/32     0100:1/16     0011:1/8     0010:1/4     0001:1/2     0000:スルー(分周なし) | 0000  |   |   |

# 8.12. クロックコントロールレジスタ8[Adr.0Bh]

カウンタモジュール2のクロックの設定を行います。

表29.クロックコントロールレジスタ8

| bit | 名称         | 機能                                       | リセット値 | R | W |

|-----|------------|------------------------------------------|-------|---|---|

| 7   | CNT2CLKSEL | カウンタモジュール2の原振を選択します。<br>1:PCLK<br>0:SCLK | 0     |   |   |

| 6:4 | 予約         |                                          | 000   |   | × |

| 3:0 | CNT2CLKDIV | カウンタモジュール2に供給するクロックの分周設定をします。            | 0000  |   |   |

# 8.13. クロックコントロールレジスタ9[Adr.0Ch]

カウンタモジュール3のクロックの設定を行います。

### 表30.クロックコントロールレジスタ9

| bit | 名称         | 機能                                       | リセット値 | R | W |

|-----|------------|------------------------------------------|-------|---|---|

| 7   | CNT3CLKSEL | カウンタモジュール3の原振を選択します。<br>1:PCLK<br>0:SCLK | 0     |   |   |

| 6:4 | 予約         |                                          | 000   |   | × |

| 3:0 | CNT3CLKDIV | カウンタモジュール3に供給するクロックの分周設定をします。            | 0000  |   |   |

# 8.14. 割り込みステータスレジスタ0[Adr.0Dh]

各ブロックからの割り込み要求の有無を読み出すことができます。 各ブロック内の詳細な割り込み要因は該当ブロックの割り込みステータスレジスタを読み出して〈ださい。

表31.割り込みステータスレジスタ0

| bit | 名称        | 機能                                                        | リセット値 | R | W |

|-----|-----------|-----------------------------------------------------------|-------|---|---|

| 7:5 | 予約        |                                                           | 000   |   | × |

| 4   | INTS_IRRC | 赤外線リモコンブロックからの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 3   | INTSPWM   | PWMブロックからの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし     | 0     |   | × |

| 2   | INTSSPI   | SPIブロックからの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし     | 0     |   | × |

| 1   | INTSI2C   | I2Cブロックからの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし     | 0     |   | × |

| 0   | INTSPA    | ポートA[3:0]からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし   | 0     |   | × |

33

# 8.15. **割り込み**ステータスレジスタ1[Adr. 0 Eh]

各ブロックからの割り込み要求の有無を読み出すことができます。 各ブロック内の詳細な割り込み要求は各ブロックの割り込みステータスレジスタを読み出して〈ださい。

表32.割り込みステータスレジスタ1

| bit | 名称        | 機能                                                       | リセット値 | R | W |

|-----|-----------|----------------------------------------------------------|-------|---|---|

| 7   | INTSCNT3  | カウンタモジュール3からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 6   | INTSCNT2  | カウンタモジュール2からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 5   | INTSCNT1  | カウンタモジュール1からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 4   | INTSCNT0  | カウンタモジュール0からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 3   | INTSURT3  | UARTモジュール3からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 2   | INTS_URT2 | UARTモジュール2からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 1   | INTS_URT1 | UARTモジュール1からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

| 0   | INTSURT0  | UARTモジュール0からの割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0     |   | × |

# 8.16. **割り込みイネーブルレジスタ0**[Adr. 0Fh]

各ブロックからHINTBへの割り込み出力要求を許可します。

### 表33.割り込みイネーブルレジスタ0

| bit | 名称         | 機能                                                      | リセット値 | R | W |

|-----|------------|---------------------------------------------------------|-------|---|---|

| 7:5 | 予約         |                                                         | 000   |   | × |

| 4   | INTEN_IRRC | 赤外線リモコンブロックからの割り込み要求を許可します。<br>1:割り込み要求有効<br>0:割り込み要求無効 | 0     |   |   |

| 3   | INTENPWM   | PWMブロックからの割り込み要求を許可します。<br>1:割り込み要求有効<br>0:割り込み要求無効     | 0     |   |   |

| 2   | INTEN_SPI  | SPIブロックからの割り込み要求を許可します。<br>1:割り込み要求有効<br>0:割り込み要求無効     | 0     |   |   |

| 1   | INTENI2C   | I2Cプロックからの割り込み要求を許可します。<br>1:割り込み要求有効<br>0:割り込み要求無効     | 0     |   |   |

| 0   | INTENPA    | ポートA[3:0]からの割り込み要求を許可します。<br>1:割り込み要求有効<br>0:割り込み要求無効   | 0     |   |   |

# 8.17. **割り込みイネーブルレジスタ1**[Adr. 10h]

各ブロックからHINTBへの割り込み出力要求を許可します。

表34.割り込みイネーブルレジスタ1

| bit | 名称        | 機能                         | リセット値 | R | W |

|-----|-----------|----------------------------|-------|---|---|

|     |           | カウンタモジュール3からの割り込み要求を許可します。 |       |   |   |

| 7   | INTENCNT3 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | カウンタモジュール2からの割り込み要求を許可します。 |       |   |   |

| 6   | INTENCNT2 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | カウンタモジュール1からの割り込み要求を許可します。 |       |   |   |

| 5   | INTENCNT1 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | カウンタモジュール0からの割り込み要求を許可します。 |       |   |   |

| 4   | INTENCNT0 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | UARTモジュール3からの割り込み要求を許可します。 |       |   |   |

| 3   | INTENURT3 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | UARTモジュール2からの割り込み要求を許可します。 |       |   |   |

| 2   | INTENURT2 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | UARTモジュール1からの割り込み要求を許可します。 |       |   |   |

| 1   | INTENURT1 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

|     |           | UARTモジュールOからの割り込み要求を許可します。 |       |   |   |

| 0   | INTENURT0 | 1:割り込み要求有効                 | 0     |   |   |

|     |           | 0:割り込み要求無効                 |       |   |   |

# 8.18. 端子グループB機能選択レジスタ[Adr.11h]

端子グループBの機能を選択します。

### 表35.端子グループB機能選択レジスタ

| bit | 名称    | 機能                                                                            | リセット値 | R | W |

|-----|-------|-------------------------------------------------------------------------------|-------|---|---|

| 7   | GBPF7 | 端子グループB[11:10]に割り当てる機能を選択します。<br>1:UARTモジュール3(URT3RX、URT3TX)<br>0:ポートB[11:10] | 0     |   |   |

| 6   | GBPF6 | 端子グループB[9:8]に割り当てる機能を選択します。<br>1:UARTモジュール2(URT2RX、URT2TX)<br>0:ポートB[9:8]     | 0     |   |   |

| 5   | GBPF5 | 端子グループB[7:6]に割り当てる機能を選択します。<br>1:UARTモジュール1(URT1RX、URT1TX)<br>0:ポートB[7:6]     | 0     |   |   |

| 4   | GBPF4 | 端子グループB[5:4]に割り当てる機能を選択します。<br>1:UARTモジュール0(URT0RX、URT0TX)<br>0:ポートB[5:4]     | 0     |   |   |

| 3   | GBPF3 | 端子グループB[3]に割り当てる機能を選択します。<br>1:赤外線リモコンモジュール<br>0:ポートB[3]                      | 0     |   |   |

| 2   | GBPF2 | 端子グループB[2]に割り当てる機能を選択します。<br>1:PWMモジュール2<br>0:ポートB[2]                         | 0     |   |   |

| 1   | GBPF1 | 端子グループB[1]に割り当てる機能を選択します。<br>1:PWMモジュール1<br>0:ポートB[1]                         | 0     |   |   |

| 0   | GBPF0 | 端子グループB[0]に割り当てる機能を選択します。<br>1:PWMモジュール0<br>0:ポートB[0]                         | 0     |   |   |

# 8.19. 端子グループC機能選択レジスタ[Adr.12h]

端子グループCの機能を選択します。

### 表36. 端子グループC機能選択レジスタ

| bit | 名称    | 機能                                                                                                                   | リセット値 | R | W |

|-----|-------|----------------------------------------------------------------------------------------------------------------------|-------|---|---|

| 7:6 | 予約    |                                                                                                                      | 0000  |   | × |

| 5:4 | GCPF2 | 端子グループC[11:8]に割り当てる機能を選択します。 11:I2Cポート5&4(I2CSDA、I2CSCL) 10:SPIポート2(SPISCS、SPISDO、SPISDI、SPISCK) 01:予約 00:ポートC[11:8] | 00    |   |   |

| 3:2 | GCPF1 | 端子グループC[7:4]に割り当てる機能を選択します。 11:I2Cポート3&2(I2CSDA、I2CSCL) 10:SPIポート1(SPISCS、SPISDO、                                    | 00    |   |   |

| 1:0 | GCPF0 | 端子グループC[3:0]に割り当てる機能を選択します。 11:I2Cポート1&0(I2CSDA、I2CSCL) 10:SPIポート0(SPISCS、SPISDO、                                    | 00    |   |   |

# 8.20. プロックスタンバイレジスタ0[Adr.13h]

各ブロック(I2C、SPI、UART)のクロック供給を有効にします。

## 表37.ブロックスタンバイレジスタ0

| bit | 名称     | 機能                                        | リセット値 | R | W |

|-----|--------|-------------------------------------------|-------|---|---|

| 7   | URT3ON | UARTモジュール3のクロック供給を有効にします。<br>1:有効<br>0:停止 | 0     |   |   |

| 6   | URT2ON | UARTモジュール2のクロック供給を有効にします。<br>1:有効<br>0:停止 | 0     |   |   |

| 5   | URT1ON | UARTモジュール1のクロック供給を有効にします。<br>1:有効<br>0:停止 | 0     |   |   |

| 4   | URT0ON | UARTモジュール0のクロック供給を有効にします。<br>1:有効<br>0:停止 | 0     |   |   |

| 3:2 | 予約     |                                           | 0 0   |   | × |

| 1   | SPION  | S P I プロックのクロック供給を有効にします。<br>1:有効<br>0:停止 | 0     |   |   |

| 0   | I2CON  | I2Cプロックのクロック供給を有効にします。<br>1:有効<br>0:停止    | 0     |   |   |

# 8.21. プロックスタンバイレジスタ1[Adr.14h]

各ブロック(PWM、赤外線リモコン、カウンタ)のクロック供給を有効にします。

### 表38.ブロックスタンバイレジスタ1

| bit | 名称     | 機能                                         | リセット値 | R | W |

|-----|--------|--------------------------------------------|-------|---|---|

| 7   | CNT3ON | カウンタモジュール3のクロック供給を有効にします。<br>1:有効<br>0:停止  | 0     |   |   |

| 6   | CNT2ON | カウンタモジュール2のクロック供給を有効にします。<br>1:有効<br>0:停止  | 0     |   |   |

| 5   | CNT10N | カウンタモジュール1のクロック供給を有効にします。<br>1:有効<br>0:停止  | 0     |   |   |

| 4   | CNTOON | カウンタモジュール0のクロック供給を有効にします。<br>1:有効<br>0:停止  | 0     |   |   |

| 3   | IRRCON | 赤外線リモコンブロックのクロック供給を有効にします。<br>1:有効<br>0:停止 | 0     |   |   |

| 2   | PWM2ON | PWMモジュール2のクロック供給を有効にします。<br>1:有効<br>0:停止   | 0     |   |   |

| 1   | PWM10N | PWMモジュール1のクロック供給を有効にします。<br>1:有効<br>0:停止   | 0     |   |   |

| 0   | PWM0ON | PWMモジュール0のクロック供給を有効にします。<br>1:有効<br>0:停止   | 0     |   |   |

## 8.22. ポートアサインレジスタ[Adr. 15h]

I2C、SPIを割り当てるポートを設定します。なお、端子グループC機能選択レジスタ[Adr.12h]でSPIに設定され、かつ、本レジスタSPIPASで選択されていないSPIポートにつきましては、Hi - Z状態になります。

表39.ポートアサインレジスタ

| bit | 名称         | 機能                                                                                                                                | リセット値 | R | W |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|---|---|

| 7:6 | 予約         |                                                                                                                                   | 0 0   |   | × |

| 5:4 | SPIPAS     | SPIプロックを割り当てるポート番号を指定します。<br>11:非選択<br>10:SPI2を使用<br>01:SPI1を使用<br>00:SPI0を使用                                                     | 11    |   |   |

| 3   | 予約         |                                                                                                                                   | 0     |   | × |

| 2:0 | I2 C P A S | I2Cプロックを割り当てるポート番号を指定します。<br>110~111:予約<br>101:I2C5を使用<br>100:I2C4を使用<br>011:I2C3を使用<br>010:I2C2を使用<br>001:I2C1を使用<br>000:I2C0を使用 | 000   |   |   |

## 8.23. UARTJレープバックレジスタ[Adr.16h]

ソフトウェアのテスト用にUARTのモジュール0と1及び2と3をループバック接続します。外部端子は、他の設定にしたがいます。

表40.UARTループバックレジスタ

|   | bit | 名称         | 機能                                                | リセット値  | R | W |

|---|-----|------------|---------------------------------------------------|--------|---|---|

| I | 7:2 | 予約         |                                                   | 000000 |   | × |

|   | 1   | UART32LOOP | モジュール2と3をループバック接続します。<br>1:ループバック接続<br>0:通常(独立使用) | 0      |   |   |

|   | 0   | UART10LOOP | モジュール0と1をループバック接続します。<br>1:ループバック接続<br>0:通常(独立使用) | 0      |   |   |

## 8.24. ポートA方向設定レジスタ[Adr. 20h]

ポートAの方向を設定します。

#### 表41.ポートA方向設定レジスタ

| bit | 名称         | 機能                                        | リセット値 | R | W |

|-----|------------|-------------------------------------------|-------|---|---|

| 7:4 | 予約         |                                           | 0000  |   | × |

| 3:0 | PADIR[3:0] | ポートA[3:0]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 1111  |   |   |

## 8.25. ポートAデータレジスタ[Adr. 21h]

ポートAの出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

### 表 42.ポートA データレジスタ

| bit | 名称          | 機能                                     | リセット値 | R | W |

|-----|-------------|----------------------------------------|-------|---|---|

| 7:4 | 予約          |                                        | 0000  |   | × |

| 3:0 | PADAT [3:0] | ポートA[3:0]の出力データを設定します。また、端子の状態を読み出します。 | 0000  |   |   |

# 8.26. ポートA割り込みステータスレジスタ[Adr. 22h]

ポートAの割り込みのステータスを示します。ステータスは"1"にセットされているときに"1"を書くとクリアされます。

#### 表43.ポートA割り込みステータスレジスタ

| bit | 名称          | 機能                                                    | リセット値 | R | W |

|-----|-------------|-------------------------------------------------------|-------|---|---|

| 7:4 | 予約          |                                                       | 0000  |   | × |

| 3:0 | PAINTF[3:0] | ポートA[3:0]の割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0000  |   |   |

# 8.27. ポートA割り込みイネーブルレジスタ[Adr. 23h]

ポートAの割り込み要求を許可します。

### 表44.ポートA割り込みイネーブルレジスタ

| I | bit | 名称           | 機能                                                   | リセット値 | R | W |

|---|-----|--------------|------------------------------------------------------|-------|---|---|

|   | 7:4 | 予約           |                                                      | 0000  |   | × |

|   | 3:0 | PAINTEN[3:0] | ポートA [3:0]の割り込み要求を許可します。<br>1:割り込み要求有効<br>0:割り込み要求無効 | 0000  |   |   |

# 8.28. ポートA割り込みエッジ選択レジスタ[Adr.24h]

ポートAの割り込みエッジを選択します。

### 表45.ポートA割り込みエッジ選択レジスタ

|   | bit | 名称           | 機能                                                   | リセット値 | R | W |

|---|-----|--------------|------------------------------------------------------|-------|---|---|

| I | 7:4 | 予約           |                                                      | 0000  |   | × |

|   | 3:0 | PAINTEG[3:0] | ポートA[3:0]の割り込みエッジを選択します。<br>1:立ち上がりエッジ<br>0:立ち下がりエッジ | 0000  |   |   |

## 8.29. ポートB方向設定レジスタ\_\_L[Adr. 25h]

ポートB[7:0]の方向を設定します。

#### 表46.ポートB方向設定レジスタ\_\_L

| bit | 名称         | 機能                                        | リセット値    | R | W |

|-----|------------|-------------------------------------------|----------|---|---|

| 7:0 | PBDIR[7:0] | ポートB[7:0]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 11111111 |   |   |

## 8.30. ポートB方向設定レジスタ\_\_H[Adr. 26h]

ポートB[11:8]の方向を設定します。

### 表47.ポートB方向設定レジスタ\_\_H

| bit | 名称          | 機能                                         | リセット値 | R | W |

|-----|-------------|--------------------------------------------|-------|---|---|

| 7:4 | 予約          |                                            | 0000  |   | × |

| 3:0 | PBDIR[11:8] | ポートB[11:8]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 1111  |   |   |

# 8.31. ポートBデータレジスタ\_\_L[Adr.27h]

ポートB[7:0]の出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

### 表 48.ポートBデータレジスタ\_\_L

| bit | 名称         | 機能                                     | リセット値   | R | W |

|-----|------------|----------------------------------------|---------|---|---|

| 7:0 | PBDAT[7:0] | ポートB[7:0]の出力データを設定します。また、端子の状態を読み出します。 | 0000000 |   |   |

## 8.32. ポートBデータレジスタ\_\_H[Adr. 28h]

ポートB[11:8]の出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

表 49. ポートBデータレジスタ\_\_H

| bit | 名称          | 機能                                          | リセット値 | R | W |

|-----|-------------|---------------------------------------------|-------|---|---|

| 7:4 | 予約          |                                             | 0000  |   | × |

| 3:0 | PBDAT[11:8] | ポートB[11:8]の出力データを設定します。また、端子の<br>状態を読み出します。 | 0000  |   |   |

# 8.33. ポートC方向設定レジスタ\_\_L[Adr.29h]

ポートC[7:0]の方向を設定します。

#### 表50.ポートC方向設定レジスタ\_\_L

| ĺ | bit | 名称          | 機能                                        | リセット値    | R | W |

|---|-----|-------------|-------------------------------------------|----------|---|---|

|   | 7:0 | PC DIR[7:0] | ポートC[7:0]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 11111111 |   |   |

## 8.34. ポートC方向設定レジスタ\_\_H[Adr. 2Ah]

ポートC[11:8]の方向を設定します。

### 表51.ポートC方向設定レジスタ\_\_H

| bit | 名称          | 機能                                         | リセット値 | R | W |

|-----|-------------|--------------------------------------------|-------|---|---|

| 7:4 | 予約          |                                            | 0000  |   | × |

| 3:0 | PCDIR[11:8] | ポートC[11:8]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 1111  |   |   |

## 8.35. ポートC データレジスタ\_\_L [ A dr . 2 B h ]

ポートC[7:0]の出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

### 表52.ポートCデータレジスタ\_\_L

| I | bit | 名称         | 機能                                     | リセット値   | R | W |

|---|-----|------------|----------------------------------------|---------|---|---|

|   | 7:0 | PCDAT[7:0] | ポートC[7:0]の出力データを設定します。また、端子の状態を読み出します。 | 0000000 |   |   |

## 8.36. ポートCデータレジスタ\_\_H[Adr. 2Ch]

ポートC[11:8]の出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

#### 表53.ポートCデータレジスタ\_\_H

| I | bit | 名称          | 機能                                           | リセット値 | R | W |

|---|-----|-------------|----------------------------------------------|-------|---|---|

| I | 7:4 | 予約          |                                              | 0000  |   | × |

|   | 3:0 | PCDAT[11:8] | ポートC [11:8]の出力データを設定します。また、端子の<br>状態を読み出します。 | 0000  |   |   |

# 8.37. ポートD方向設定レジスタ\_\_L[Adr. 2Dh]

ポートD[7:0]の方向を設定します。

### 表54.ポートD方向設定レジスタ\_\_L

| bit | 名称         | 機能                                        | リセット値    | R | W |

|-----|------------|-------------------------------------------|----------|---|---|

| 7:0 | PDDIR[7:0] | ポートD[7:0]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 11111111 |   |   |

## 8.38. ポートD方向設定レジスタ\_\_H[Adr. 2 Eh]

ポートD[11:8]の方向を設定します。

### 表55.ポートD方向設定レジスタ\_\_H

| I | bit | 名称          | 機能                                         | リセット値 | R | W |

|---|-----|-------------|--------------------------------------------|-------|---|---|

| Ī | 7:4 | 予約          |                                            | 0000  |   | × |

|   | 3:0 | PDDIR[11:8] | ポートD[11:8]の入力/出力の方向を設定します。<br>1:入力<br>0:出力 | 1111  |   |   |

## 8.39. ポートDデータレジスタ\_\_L[Adr. 2Fh]

ポートD[7:0]の出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

### 表56.ポートDデータレジスタ\_\_L

| bit | 名称         | 機能                                     | リセット値    | R | W |

|-----|------------|----------------------------------------|----------|---|---|

| 7:0 | PDDAT[7:0] | ポートD[7:0]の出力データを設定します。また、端子の状態を読み出します。 | 00000000 |   |   |

# 8.40. ポートDデータレジスタ\_\_H[Adr.30h]

ポートD[11:8]の出力データを設定します。また、本レジスタをリードすることにより、端子の状態を読み出すことも出来ます。

### 表57.ポートDデータレジスタ\_\_H

|   | bit | 名称          | 機能                                          | リセット値 | R | W |

|---|-----|-------------|---------------------------------------------|-------|---|---|

| Ī | 7:4 | 予約          |                                             | 0000  |   | × |

|   | 3:0 | PDDAT[11:8] | ポートD[11:8]の出力データを設定します。また、端子の<br>状態を読み出します。 | 0000  |   |   |

## 8.41. [2 C プリスケールレジスタ\_\_L [ A dr . 4 0 h ]

I2Cプロックに供給されているクロックを分周し、SCLの周波数を決定します。設定可能な値は16bitで、40hに下位byte、41hに上位byteを設定します。SCLの出力クロックと設定値との関係は以下のようになります。

Pscl = プリスケールレジスタ設定値 iCLK = I2Cブロック供給クロック(Hz) SCL = I2Cバス出力クロック(Hz)

$$Pscl = \frac{iCLK}{5*SCL} - 1$$

Psclには、0000h以外の値を設定してください。

### 表58.I2Cプリスケールレジスタ\_\_L

| I | bit | 名称           | 機能                                    | リセット値    | R | W |

|---|-----|--------------|---------------------------------------|----------|---|---|

|   | 7:0 | I2 C P R E L | SCLの周波数を決定するためのプリスケール値(下位byte)を設定します。 | 00000001 |   |   |

### 8.42. [2 C プリスケールレジスタ\_\_\_H [ A dr . 4 1 h ]

SCLの周波数を決定するためのプリスケール値(上位byte)を設定します。

表59.12Cプリスケールレジスタ\_\_H

| bit | 名称      | 機能                                    | リセット値   | R | W |

|-----|---------|---------------------------------------|---------|---|---|

| 7:0 | I2CPREH | SCLの周波数を決定するためのプリスケール値(上位byte)を設定します。 | 0000000 |   |   |

## 8.43. [2 C割り込みイネーブルレジスタ[Adr. 42h]

I2Cバスの転送完了時の割り込みを設定します。

表60.12 C割り込みイネーブルレジスタ

| bit | 名称        | 機能                                                  | リセット値   | R | W |

|-----|-----------|-----------------------------------------------------|---------|---|---|

| 7:1 | 予約        |                                                     | 0000000 |   | × |

| 0   | I2 CINTEN | I2Cバスの転送完了時の割り込みを設定します。<br>1:割り込み要求有効<br>0:割り込み要求無効 | 0       |   |   |

### 8.44. [2 C割り込みステータスレジスタ[Adr. 43h]

I2Cバスの割り込みステータスを示します。ステータスは"1"にセットされているときに"1"を書くとクリアされます。

表61.12 C割り込みステータスレジスタ

| I | bit | 名称        | 機能                                                | リセット値   | R | W |

|---|-----|-----------|---------------------------------------------------|---------|---|---|

|   | 7:1 | 予約        |                                                   | 0000000 |   | × |

|   | 0   | I2 CINTST | 転送完了時の割り込み要求の有無を示します。<br>1:割り込み要求あり<br>0:割り込み要求なし | 0       |   |   |

## 8.45. [2 C送信データレジスタ[Adr. 44h]

I2Cバスで転送するデータを設定します。このレジスタは、スレーブアドレス送信時とデータ送信時で以下のようにbitの意味が変わりますのでご注意ください。

表62.12 C送信データレジスタ(スレーブアドレス送信時)

| bit | 名称       | 機能                                                | リセット値   | R | W |

|-----|----------|---------------------------------------------------|---------|---|---|

| 7:1 | I2CSAD   | スレープアドレスを設定します。                                   | 0000000 |   |   |

| 0   | I2 C R W | リード/ライトbit <b>を設定します。</b><br>1:リードbit<br>0:ライトbit | 0       |   |   |

#### 表 83.12 C送信データレジスタ(データ送信時)

| ĺ | bit | 名称       | 機能           | リセット値    | R | W |

|---|-----|----------|--------------|----------|---|---|

| I | 7:0 | I2CTRDAT | 送信データを設定します。 | 00000000 |   |   |

## 8.46. [2C受信データレジスタ[Adr.45h]

I2Cバスから受信したデータを読み出すために使用されます。

表64.12 C受信データレジスタ

| I | bit | 名称       | 機能                     | リセット値    | R | W |

|---|-----|----------|------------------------|----------|---|---|

|   | 7:0 | I2CRVDAT | I2Cバスから受信したデータを読み出します。 | 00000000 |   | × |

## 8.47. [2 Cコマンドレジスタ[Adr. 46h]

I2Cバスに発行するコマンドを決定します。bit[7:4]はコマンド実行後、自動的にクリアされます。なお、bit[5]とbit[4]は同時に"1"にしないでください。

表65.I2Cコマンドレジスタ

| bit | 名称       | 機能                                                | リセット値 | R | W |

|-----|----------|---------------------------------------------------|-------|---|---|

| 7   | I2CSTART | "1"を書くとスタートコンディションを生成します。                         | 0     |   |   |

| 6   | I2CSTOP  | "1"を書くとストップコンディションを生成します。                         | 0     |   |   |

| 5   | I2CRD    | "1"を書くとスレーブからデータを受信します。                           | 0     |   |   |

| 4   | I2CWR    | "1"を書くとデータをスレーブに対して送信します。                         | 0     |   |   |

| 3   | I2CACK   | レシーバのときにACKを送るかNACKを送るかを決定します。<br>1:NACK<br>0:ACK | 0     |   |   |

| 2:0 | 予約       |                                                   | 000   |   | × |

## 8.48. [2 Cステータスレジスタ[Adr. 47h]

このレジスタは 12 Cバス上のステータスを示します。

表66.I2Cステータスレジスタ

| bit | 名称         | 機能                                                                                                                                                    | リセット値  | R | W |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---|---|

| 7:2 | 予約         |                                                                                                                                                       | 000000 |   | × |

| 1   | I2CRXACK   | アクノリッジが受信されない場合、転送完了時にこのbitが<br>セットされます。なお、レシーバの時にI2CACKを"1"(NA<br>CK)に設定した場合もこのbitは"1"にセットされますのでご<br>注意ください。<br>1:アクノリッジを受信していません<br>0:アクノリッジを受信しました | 0      |   | × |

| 0   | I2 C T I P | 転送状況を示します。<br>1:転送実行中<br>0:転送完了                                                                                                                       | 0      |   | × |

## 8.49. SPIコントロールレジスタ[Adr.50h]

SPIブロックの動作を決定します。

表67.SPIコントロールレジスタ

| bit | 名称        | 機能                                                         | リセット値 | R | W |

|-----|-----------|------------------------------------------------------------|-------|---|---|

| 7:5 | 予約        |                                                            | 0 0 0 |   | × |

| 4   | SPISCSPOL | SPISCSの論理を決定します。<br>1:正論理<br>0:負論理                         | 0     |   |   |

| 3   | SPIASCS   | SPI_SCSのアサート方法を決定します。<br>1:マニュアル<br>0:オート                  | 0     |   |   |