# ZEN0317P データシート

株式会社ジーニック

Left blank

## 目次

| 1 | . 概要                                                  | 1  |

|---|-------------------------------------------------------|----|

| 2 | . 特徵                                                  | 1  |

| 2 | . システムブロック構成                                          | 2  |

| J | . フヘナムノロッノ相以                                          |    |

| 4 | . 端子一覧                                                | 3  |

|   | 4.1. 機能信号                                             | 3  |

|   | 4.2. 電源·グランド端子                                        | 3  |

| 5 | . 機能                                                  |    |

|   | 5.1. 上限値カウント                                          | 4  |

|   | 5.2.カウントパルス選択                                         | 4  |

|   | 5.3. プリスケール                                           | 4  |

|   | 5.4. カウンタロード                                          |    |

|   | 5.5.カウンタ動作 / 停止                                       |    |

|   | 5.6. カウントラッチ                                          |    |

|   | 5.6.1.カウンタ読み出し自動ラッチ                                   |    |

|   | 5.6.2. コマンド書き込みラッチ                                    |    |

|   | 5.6.3. 外部端子ラッチ                                        |    |

|   | 5.7. カウントクリア                                          |    |

|   | 5.7.1.コマンド書き込みクリア                                     |    |

|   | 5.7.2.外部端子クリア                                         |    |

|   |                                                       |    |

| 6 | . レジスタ                                                |    |

|   | 6.1. アドレスマッピング                                        | 7  |

|   | 6.2.カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.0](下位byte)[Adr.00h] |    |

|   | 6.3.カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.0](上位byte)[Adr.01h] | 8  |

|   | 6.4.カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.1](下位byte)[Adr.02h] |    |

|   | 6.5.カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.1](上位byte)[Adr.03h] |    |

|   | 6.6.カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.2](下位byte)[Adr.04h] |    |

|   | 6.7.カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.2](上位byte)[Adr.05h] |    |

|   | 6.8. 上限値設定レジスタ[ch.0](下位byte)[Adr.06h]                 |    |

|   | 6.9. 上限値設定レジスタ[ch.0](上位byte)[Adr.07h]                 |    |

|   | 6.10. 上限値設定レジスタ[ch.1](下位byte)[Adr.08h]                |    |

|   | 6.11. 上限値設定レジスタ[ch.1](上位byte)[Adr.09h]                |    |

|   | 6.12. 上限値設定レジスタ[ch.2](下位byte)[Adr.0Ah]                |    |

|   | 6.13. 上限値設定レジスタ[ch.2](上位byte)[Adr.0Bh]                |    |

|   | 6.14. 動作設定レジスタ[ch.0-2][Adr.0C-0Eh]                    | 12 |

| 6.15. ラッチ / クリアコマンドレジスタ(書き込み) [Adr. 0Fh]     | 13 |

|----------------------------------------------|----|

| 6.16. <b>外部制御入力ステータスレジスタ(読み出</b> し)[Adr.0Fh] | 14 |

| 7. 電気的特性                                     | 15 |

| 7.1. 絶対最大定格                                  | 15 |

| 7.2. 推奨動作条件                                  | 15 |

| 7.3. 直流特性                                    | 15 |

| 7.4. 交流特性                                    | 16 |

| 7.5. タイミングダイアグラム                             | 17 |

| 7.5.1. ライトサイクル                               | 17 |

| 7.5.2. リードサイクル                               | 17 |

| 7.5.3.外部カウントパルス入力                            | 18 |

| 7.5.4.外部ラッチ入力                                | 18 |

| 7.5.5. 外部クリア入力                               | 18 |

| 7.5.6. リセット入力                                | 18 |

| 8. パッケージ形状                                   | 19 |

| 9. 備考                                        | 20 |

| 10 改訂履歴                                      | 21 |

#### 1. 概要

ZENO317P は最大カウント応答速度17.5Mcps(システムクロック分周パルス使用時)の16bitアップカウンタを3ch.内蔵した同期式カウンタICです。カウンタ値を安定して読み取るためにラッチレジスタを装備しており、ラッチレジスタへのカウンタ値の転送はカウンタ読み出し、ラッチコマンド書き込み及び外部端子ラッチの3通りの方法から選択可能です。また、カウンタのクリア動作はクリアコマンド書き込み及び外部端子クリアの2通りの方法から選択可能です。

カウンタは16bitのフリーラン動作だけでなく、上限値レジスタによりカウント動作の上限を任意に設定可能です。

カウントパルス入力は外部パルス入力とシステムクロック分周パルスのいずれかから選択可能です。また、外部パルス入力 及びシステムクロック分周パルスのいずれに対しても適用可能なプリスケーラを各チャンネル個別に用意しています。さらにノ イズによる誤動作を防止するために外部パルス入力に対して有効なデジタルフィルタを内蔵しています。

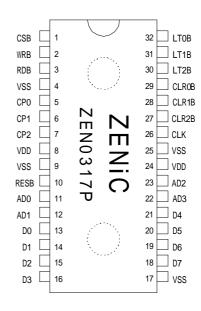

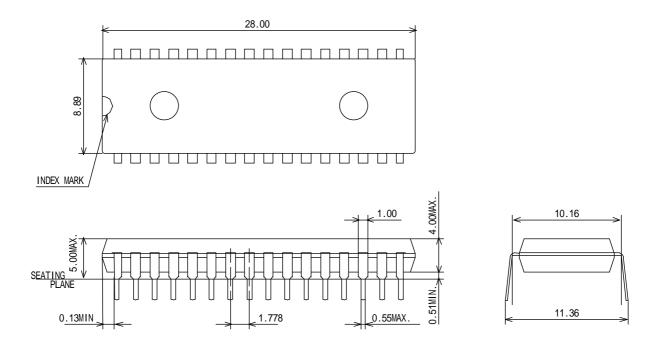

パッケージには基板サイズの小型化が可能な32ピン400milシュリンクDIPを採用しています。

#### 2. 特徵

bit幅 : 16bit チャンネル数 : 3ch.

最大カウンタ応答速度 : 外部入力パルス時 - 15Mcps(システムクロックfo = 35MHz時)

: システムクロック分周パルス時 - 17.5 Mcps(fo = 35 MHz時)

カウントパルス周波数 : 外部入力パルス時 - DC ~ 15MHz(fo × 1 / 2 以内)

カウンタ値ラッチ機能・・・カウンタ読み出し自動ラッチ、ラッチコマンド書き込み及び外部ラッチ端子

カウンタ値クリア機能・・クリアコマンド書き込み及び外部クリア端子

上限値カウント機能: カウンタの上限値を設定可(0~上限値の間でカウントを継続)

プリスケール機能: : OFF / 2 / 4 / 8

デジタルフィルタ機能 : OFF / システムクロック2周期幅以上有効 パッケージ : 32ピン400milシュリンクDIP(10.16×28mm)

電源電圧 :5 V 単一

図1.端子配置図(Top View)

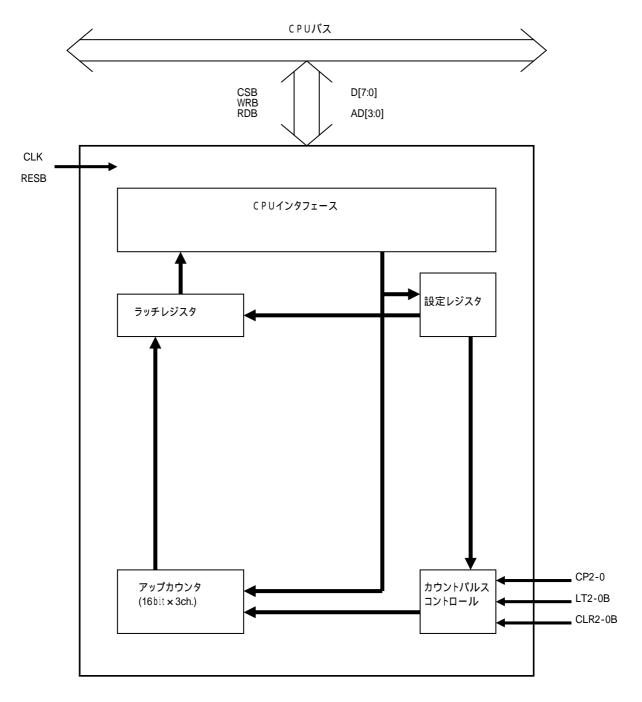

## 3. システムブロック構成

図2.ブロック図

# 4. 端子一覧

## 4.1. 機能信号

表 1. 機能信号端子一覧表

| ピン番号 | 記号    | 信 <del>号</del> 名     | 属性                        | 機能                                     |

|------|-------|----------------------|---------------------------|----------------------------------------|

| 2 2  | AD[3] |                      |                           |                                        |

| 23   | AD[2] | Address Bus          | IN                        | <br>  カウンタ及び内部レジスタを選択します。              |

| 12   | AD[1] | Audiess bus          | 111                       | リカラング及の内部レンスグを選択しより。                   |

| 11   | AD[0] |                      |                           |                                        |

| 18   | D[7]  |                      |                           |                                        |

| 19   | D[6]  |                      |                           |                                        |

| 20   | D[5]  |                      |                           |                                        |

| 21   | D[4]  | Data Bus             | <br>  INOUT   双方向データバスです。 | │<br>  双方向データバスです                      |

| 16   | D[3]  |                      | 111001                    | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| 15   | D[2]  |                      | 1                         |                                        |

| 14   | D[1]  |                      |                           |                                        |

| 13   | D[0]  |                      |                           |                                        |

| 1    | CSB   | Chip Select          | IN                        | デバイス選択のためのチップセレクト入力です。                 |

| 3    | RDB   | Read Strobe          | IN                        | データを読み出すためのストローブ入力です。                  |

| 2    | WRB   | <b>W</b> rite Strobe | IN                        | データを書き込むためのストローブ入力です。                  |

| 7    | CP2   | Count Pulse          | IN                        | カウントパルス入力(ch.2)です。                     |

| 6    | CP1   | Count Pulse          | IN                        | カウントパルス入力(ch.1)です。                     |

| 5    | CP0   | Count Pulse          | IN                        | カウントパルス入力(ch.0)です。                     |

| 30   | LT2B  | External Latch       | IN                        | 外部ラッチ入力(ch.2)です。                       |

| 31   | LT1B  | External Latch       | IN                        | 外部ラッチ入力(ch.1)です。                       |

| 32   | LT0B  | External Latch       | IN                        | 外部ラッチ入力(ch.0)です。                       |

| 27   | CLR2B | External Clear       | IN                        | 外部クリア入力(ch.2)です。                       |

| 28   | CLR1B | External Clear       | IN                        | 外部クリア入力(ch.1)です。                       |

| 2 9  | CLROB | External Clear       | IN                        | 外部クリア入力(ch.0)です。                       |

| 26   | CLK   | System Clock         | IN                        | システムクロック入力です。                          |

| 10   | RESB  | Master Reset         | IN                        | マスタリセット入力です。                           |

## 4.2. **電源・グランド端子**

表2.電源・グランド端子一覧表

| ピン番号               | 記号  | 信号名    | 属性 | 機能        |

|--------------------|-----|--------|----|-----------|

| 8<br>2 4           | VDD | Power  | -  | 5V電源端子です。 |

| 4<br>9<br>17<br>25 | VSS | Ground | -  | グランド端子です。 |

## 5. 機能

カウントパルスの立ち上がりをシステムクロックで検出しカウントアップします。カウントパルス入力周波数は最高15MHz(システムクロック35MHz供給時)です。詳細は7.4交流特性の項目を参照してください。

#### 5.1. 上限値カウント

カウンタの物理的なbit幅は16bit固定ですが、カウントの範囲は上限値設定レジスタによって任意に設定可能です( $0 \sim 65$  535)。たとえば、上限値の設定をMとするとカウンタ値の遷移は、

$0 \ 1 \ 2 \ 3 \cdots M-1 \ M \ 0 \ 1 \ 2 \ 3 \cdots M-1 \ M \ 0 \ 1 \cdots$

となります。

#### 5.2. カウントパルス選択

動作設定レジスタにより、カウンタに供給するカウントパルスを外部入力とシステムクロック分周パルスのいずれかから選択可能です。

#### 5.3. プリスケール

カウントパルスを(外部パルス及びシステムクロック分周パルスとも)1/2、1/4、1/8にプリスケールする機能を有しています。

#### 5.4. カウンタロード

カウンタに値を書き込むことが可能です。ただし、16bit一括では書き込めません。上位下位それぞれ8bitずつ書いてください。

#### 5.5. カウンタ動作 / 停止

チャンネルごとにカウンタの動作 / 停止を切り替えることができます。 停止の間カウンタ値は保持されます。

#### 5.6. カウントラッチ

カウンタ値のラッチレジスタへのラッチ動作にはホストアクセスによるラッチと外部端子ラッチの2種類があり、さらにホストアクセスによるラッチは動作設定レジスタで選択する、カウンタ読み出し自動ラッチとコマンド書き込みラッチの2つの方式があります。カウンタ読み出し自動ラッチを選択した場合、外部端子ラッチは無効になります。

#### 5.6.1. カウンタ読み出し自動ラッチ

ラッチレジスタの下位byteを指定して値を読み出すと、そのときの16bitのカウンタ値全体をラッチレジスタにラッチします。したがって、あるチャンネルのカウンタ値を正しく読み出すにはそのチャンネルの下位byte 上位byteの順番で読み出す必要があります。なお、本モードでは外部端子ラッチは無効になります。

#### 5.6.2. コマンド書き込みラッチ

ラッチ / クリアコマンドレジスタに書き込むことでカウンタ値全体をラッチレジスタにラッチします(複数チャンネル同時にラッチ可能です)。 本モードでは外部端子ラッチも使用可能です。

#### 5.6.3. 外部端子ラッチ

ラッチ動作用の外部端子(LTO - 2B)の立ち下がリエッジ入力で、そのときの16bitのカウンタ値全体をラッチレジスタにラッチします(複数チャンネル同時にラッチ可能です)。外部端子ラッチを使用する場合はホストアクセスによるラッチをコマンド書き込みラッチモードにしておく必要があります。

#### 5.7. カウントクリア

カウンタ値のクリア動作(カウンタ値を000hにする)にはコマンド書き込みクリアと外部端子クリアの2種類があります。両方式とも常に有効で、レジスタ設定で選択する必要はありません。

#### 5.7.1. コマンド書き込みクリア

ラッチ / クリアコマンドレジスタに書き込むことでカウンタ値をクリアします。

#### 5.7.2. 外部端子クリア

クリア動作用の外部端子(CLR0-2B)の立ち下がリエッジ入力でカウンタ値をクリアします。

### 5.8. デジタルフィルタ

カウントパルス入力(CP0 - 2)のシステムクロック2周期幅未満の変化をノイズと見なし無視することができます。この場合、有効なカウントパルス周波数がfoの1 / 4未満となりますのでご注意ください。

## 6. レジスタ

**ZEN0317Pの内部レジスタへのアクセスは外部端子**CSB、RDB、WRB、AD[3:0]、D[7:0]で行います。

### 6.1. アドレスマッピング

表3に ZEN0317P のアドレスマッピングを示します。各レジスタの詳細は6.2節以降を参照してください。

表3.アドレスマッピング

| CSB | RDB | WRB | AD[3:0](h) | <b>動作</b> (D[7:0])        |

|-----|-----|-----|------------|---------------------------|

| 1   | *   | *   | *          | ディスエーブル(データバス:Hi - Z)     |

| 0   | 0   | 1   | 0.0        | ラッチレジスタ(ch.0)下位byte読み出し   |

| 0   | 0   | 1   | 0 1        | ラッチレジスタ(ch.0)上位byte読み出し   |

| 0   | 0   | 1   | 0 2        | ラッチレジスタ(ch.1)下位byte読み出し   |

| 0   | 0   | 1   | 03         | ラッチレジスタ(ch.1)上位byte読み出し   |

| 0   | 0   | 1   | 0 4        | ラッチレジスタ(ch.2)下位byte読み出し   |

| 0   | 0   | 1   | 0.5        | ラッチレジスタ(ch.2)上位byte読み出し   |

| 0   | 0   | 1   | 06         | 上限値設定レジスタ(ch.0)下位byte読み出し |

| 0   | 0   | 1   | 07         | 上限値設定レジスタ(ch.0)上位byte読み出し |

| 0   | 0   | 1   | 0.8        | 上限値設定レジスタ(ch.1)下位byte読み出し |

| 0   | 0   | 1   | 0 9        | 上限値設定レジスタ(ch.1)上位byte読み出し |

| 0   | 0   | 1   | 0 A        | 上限値設定レジスタ(ch.2)下位byte読み出し |

| 0   | 0   | 1   | 0 B        | 上限値設定レジスタ(ch.2)上位byte読み出し |

| 0   | 0   | 1   | 0 C        | 動作設定レジスタ(ch.0)読み出し        |

| 0   | 0   | 1   | 0 D        | 動作設定レジスタ(ch.1)読み出し        |

| 0   | 0   | 1   | 0 E        | 動作設定レジスタ(ch.2)読み出し        |

| 0   | 0   | 1   | 0 F        | 外部制御入力ステータスレジスタ読み出し       |

| 0   | 1   | 0   | 0 0        | カウンタ(ch.0)下位byte書き込み      |

| 0   | 1   | 0   | 01         | カウンタ(ch.0)上位byte書き込み      |

| 0   | 1   | 0   | 02         | カウンタ(ch.1)下位byte書き込み      |

| 0   | 1   | 0   | 03         | カウンタ(ch.1)上位byte書き込み      |

| 0   | 1   | 0   | 0 4        | カウンタ(ch.2)下位byte書き込み      |

| 0   | 1   | 0   | 0.5        | カウンタ(ch.2)上位byte書き込み      |

| 0   | 1   | 0   | 0 6        | 上限値設定レジスタ(ch.0)下位byte書き込み |

| 0   | 1   | 0   | 07         | 上限値設定レジスタ(ch.0)上位byte書き込み |

| 0   | 1   | 0   | 0.8        | 上限値設定レジスタ(ch.1)下位byte書き込み |

| 0   | 1   | 0   | 0 9        | 上限値设定レジスタ(ch.1)上位byte書き込み |

| 0   | 1   | 0   | 0 A        | 上限値设定レジスタ(ch.2)下位byte書き込み |

| 0   | 1   | 0   | 0 B        | 上限値设定レジスタ(ch.2)上位byte書き込み |

| 0   | 1   | 0   | 0 C        | 動作設定レジスタ(ch.0)書き込み        |

| 0   | 1   | 0   | 0 D        | 動作設定レジスタ(ch.1)書き込み        |

| 0   | 1   | 0   | 0 E        | 動作設定レジスタ(ch.2)書き込み        |

| 0   | 1   | 0   | 0 F        | ラッチ / クリアコマンドレジスタ書き込み     |

|     |     |     |            |                           |

### 6.2. カウンタ(書き込み) / ラッチレジスタ(読み出し) [ch.0](下位byte) [Adr.00h]

カウンタ[ch.0]の下位byteの書き込み及びラッチレジスタ[ch.0]の下位byteの読み出しを行います。

#### 表4.カウンタ/ラッチレジスタ[ch.0](下位byte)

| bit | 名称      | 機能                                                          | リセット値    | R | W |

|-----|---------|-------------------------------------------------------------|----------|---|---|

| 7:0 | CNTCH0L | カウンタ[ch.0]の下位byteの書き込み及びラッチレジスタ[ch.0]<br>の下位byteの読み出しを行います。 | 00000000 |   |   |

## 6.3. カウンタ(書き込み) / ラッチレジスタ(読み出し) [ch.0](上位byte) [Adr.01h]

カウンタ[ch.0]の上位byteの書き込み及びラッチレジスタ[ch.0]の上位byteの読み出しを行います。

#### 表5.カウンタ/ラッチレジスタ[ch.0](上位byte)

| bit | 名称      | 機能                                                          | リセット値    | R | W |

|-----|---------|-------------------------------------------------------------|----------|---|---|

| 7:0 | CNTCH0H | カウンタ[ch.0]の上位byteの書き込み及びラッチレジスタ[ch.0]<br>の上位byteの読み出しを行います。 | 00000000 |   |   |

### 6.4. カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.1](下位byte)[Adr.02h]

カウンタ[ch.1]の下位byteの書き込み及びラッチレジスタ[ch.1]の下位byteの読み出しを行います。

#### 表 6. カウンタ / ラッチレジスタ[ch.1](下位byte)

| ĺ | bit | 名称      | 機能                                                          | リセット値    | R | W |

|---|-----|---------|-------------------------------------------------------------|----------|---|---|

|   | 7:0 | CNTCH1L | カウンタ[ch.1]の下位byteの書き込み及びラッチレジスタ[ch.1]<br>の下位byteの読み出しを行います。 | 00000000 |   |   |

## 6.5. カウンタ(書き込み) / ラッチレジスタ(読み出し) [ch.1](上位byte) [Adr.03h]

カウンタ[ch.1]の上位byteの書き込み及びラッチレジスタ[ch.1]の上位byteの読み出しを行います。

#### 表7.カウンタ/ラッチレジスタ[ch.1](上位byte)

| bit | 名称      | 機能                                                          | リセット値    | R | W |

|-----|---------|-------------------------------------------------------------|----------|---|---|

| 7:0 | CNTCH1H | カウンタ[ch.1]の上位byteの書き込み及びラッチレジスタ[ch.1]<br>の上位byteの読み出しを行います。 | 00000000 |   |   |

## 6.6. カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.2](下位byte)[Adr.04h]

カウンタ[ch.2]の下位byteの書き込み及びラッチレジスタ[ch.2]の下位byteの読み出しを行います。

#### 表8.カウンタ/ラッチレジスタ[ch.2](下位byte)

| I | bit | 名称      | 機能                                                          | リセット値    | R | W |

|---|-----|---------|-------------------------------------------------------------|----------|---|---|

|   | 7:0 | CNTCH2L | カウンタ[ch.2]の下位byteの書き込み及びラッチレジスタ[ch.2]<br>の下位byteの読み出しを行います。 | 00000000 |   |   |

## 6.7. カウンタ(書き込み) / ラッチレジスタ(読み出し)[ch.2](上位byte)[Adr.05h]

カウンタ[ch.2]の上位byteの書き込み及びラッチレジスタ[ch.2]の上位byteの読み出しを行います。

#### 表 9. カウンタ / ラッチレジスタ[ch. 2](上位byte)

| bit | 名称      | 機能                                                          | リセット値    | R | W |

|-----|---------|-------------------------------------------------------------|----------|---|---|

| 7:0 | CNTCH2H | カウンタ[ch.2]の上位byteの書き込み及びラッチレジスタ[ch.2]<br>の上位byteの読み出しを行います。 | 00000000 |   |   |

## 6.8. 上限値設定レジスタ[ch.0](下位byte)[Adr.06h]

カウンタ[ch.0]用上限値の下位byteを設定します。

#### 表 10. 上限値設定レジスタ[ch.0](下位byte)

| I | bit | 名称       | 機能                           | リセット値    | R | W |

|---|-----|----------|------------------------------|----------|---|---|

| I | 7:0 | ULMTCH0L | カウンタ[ch.0]用上限値の下位byteを設定します。 | 11111111 |   |   |

## 6.9. 上限値設定レジスタ[ch.0](上位byte)[Adr.07h]

カウンタ[ch.0]用上限値の上位byteを設定します。

#### 表 11. 上限値設定レジスタ[ch.0](上位byte)

| bit | 名称       | 機能                           | リセット値    | R | W |

|-----|----------|------------------------------|----------|---|---|

| 7:0 | ULMTCH0H | カウンタ[ch.0]用上限値の上位byteを設定します。 | 11111111 |   |   |

## 6.10. 上限値設定レジスタ[ch.1](下位byte)[Adr.08h]

カウンタ[ch.1]用上限値の下位byteを設定します。

#### 表 12. 上限値設定レジスタ[ch.1](下位byte)

| bit | 名称       | 機能                           | リセット値    | R | W |

|-----|----------|------------------------------|----------|---|---|

| 7:0 | ULMTCH1L | カウンタ[ch.1]用上限値の下位byteを設定します。 | 11111111 |   |   |

## 6.11. 上限値設定レジスタ[ch.1](上位byte)[Adr.09h]

カウンタ[ch.1]用上限値の上位byteを設定します。

#### 表 13. 上限値設定レジスタ[ch.1](上位byte)

| bit | 名称       | 機能                           | リセット値    | R | W |

|-----|----------|------------------------------|----------|---|---|

| 7:0 | ULMTCH1H | カウンタ[ch.1]用上限値の上位byteを設定します。 | 11111111 |   |   |

## 6.12. 上限値設定レジスタ[ch.2](下位byte)[Adr.0Ah]

カウンタ[ch.2]用上限値の下位byteを設定します。

#### 表 14. 上限値設定レジスタ[ch.2](下位byte)

| bit | 名称       | 機能                           | リセット値    | R | W |

|-----|----------|------------------------------|----------|---|---|

| 7:0 | ULMTCH2L | カウンタ[ch.2]用上限値の下位byteを設定します。 | 11111111 |   |   |

## 6.13. 上限値設定レジスタ[ch.2](上位byte)[Adr.0Bh]

カウンタ[ch.2]用上限値の上位byteを設定します。

#### 表 15. 上限値設定レジスタ[ch.2](上位byte)

| l | bit | 名称       | 機能                           | リセット値    | R | W |

|---|-----|----------|------------------------------|----------|---|---|

| I | 7:0 | ULMTCH2H | カウンタ[ch.2]用上限値の上位byteを設定します。 | 11111111 |   |   |

## 6.14. **動作設定レジスタ**[ch.0-2][Adr.0C-0Eh]

チャンネルごとに各種カウンタの動作項目を設定します。

### 表 16.動作設定レジスタ[ch.0-2]

| bit | 名称        | 機能                                                                       | リセット値 | R | W |

|-----|-----------|--------------------------------------------------------------------------|-------|---|---|

| 7:6 | 予約        |                                                                          | 0 0   |   | × |

| 5:4 | PRESCL    | プリスケーラを設定します。 11:8分周 10:4分周 01:2分周 00:無効                                 | 00    |   |   |

| 3   | SOFTLTSEL | ラッチ動作を選択します。<br>1:コマンド書き込みラッチ(外部ラッチ端子:有効)<br>0:カウンタ読み出し自動ラッチ(外部ラッチ端子:無効) | 0     |   |   |

| 2   | DFILTEREN | /イズカット用デジタルフィルタを設定します。<br>1:有効<br>0:無効                                   | 0     |   |   |

| 1   | PULSSEL   | カウントアップ用のパルスを選択します。<br>1:外部入力パルス<br>0:システムクロック分周パルス                      | 0     |   |   |

| 0   | CNTUPEN   | カウントアップ動作を制御します。カウンタの各動作設定を変更する場合はカウントアップを停止状態にしてから行ってください。  1:起動  0:停止  | 0     |   |   |

## 6.15. ラッチ / クリアコマンドレジスタ(書き込み) [Adr. 0Fh]

各チャンネルのラッチ及びクリア動作のコマンドを書き込みます。各bitは自動復帰します。なお、動作設定レジスタでそれぞれのチャンネルのコマンド書き込みラッチが選択されていない場合は本レジスタの対応するbitは無効です("1"を書き込んでもラッチされません)。

表 17. ラッチ / クリアコマンドレジスタ

| bit | 名称        | 機能                                               | リセット値 | R | W |

|-----|-----------|--------------------------------------------------|-------|---|---|

| 7   | 予約        |                                                  | Χ     | - | × |

| 6   | COMCLRCH2 | カウンタ[ch.2]の値をクリアします。<br>1:クリア実行<br>0:NOP         | 0     | - |   |

| 5   | COMCLRCH1 | カウンタ[ch.1]の値をクリアします。<br>1:クリア実行<br>0:NOP         | 0     | - |   |

| 4   | COMCLRCH0 | カウンタ[ch.0]の値をクリアします。<br>1:クリア実行<br>0:NOP         | 0     | - |   |

| 3   | 予約        |                                                  | Χ     | - | × |

| 2   | COMLTCH2  | カウンタ[ch.2]の値をラッチレジスタにラッチします。<br>1:ラッチ実行<br>0:NOP | 0     | - |   |

| 1   | COMLTCH1  | カウンタ[ch.1]の値をラッチレジスタにラッチします。<br>1:ラッチ実行<br>0:NOP | 0     | - |   |

| 0   | COMLTCH0  | カウンタ[ch.0]の値をラッチレジスタにラッチします。<br>1:ラッチ実行<br>0:NOP | 0     | - |   |

## 6.16. 外部制御入力ステータスレジスタ(読み出し)[Adr. 0Fh]

各外部制御入力のステータスを示します。入力信号の立ち下がりを検出すると対応するbitがセットされます。ただし、外部ラッチ端子(LT0 - 2B)については、動作設定レジスタで外部ラッチ機能が有効な場合のみセットされます。各bitは本アドレスを読み出すことでクリアされます。

表 18. 外部制御入力ステータスレジスタ

| bit | 名称       | 機能                                                      | リセット値 | R | W |

|-----|----------|---------------------------------------------------------|-------|---|---|

| 7   | 予約       |                                                         | 0     |   | - |

| 6   | CH2CLRST | 外部制御入力[CLR2B]のステータスを示します。<br>1:立ち下がり検出あり<br>0:立ち下がり検出なし | 0     |   | - |

| 5   | CH1CLRST | 外部制御入力[CLR1B]のステータスを示します。<br>1:立ち下がり検出あり<br>0:立ち下がり検出なし | 0     |   | _ |

| 4   | CHOCLRST | 外部制御入力[CLR0B]のステータスを示します。<br>1:立ち下がり検出あり<br>0:立ち下がり検出なし | 0     |   | - |

| 3   | 予約       |                                                         | 0     |   | - |

| 2   | CH2LTBST | 外部制御入力[LT2B]のステータスを示します。 1:立ち下がり検出あり 0:立ち下がり検出なし        | 0     |   | - |

| 1   | CH1LTBST | 外部制御入力[LT1B]のステータスを示します。 1:立ち下がり検出あり 0:立ち下がり検出なし        | 0     |   | - |

| 0   | CHOLTBST | 外部制御入力[LT0B]のステータスを示します。<br>1:立ち下がり検出あり<br>0:立ち下がり検出なし  | 0     |   | - |

## 7. 電気的特性

### 7.1. 絶対最大定格

表9.絶対最大定格( $V_{SS} = 0V$ )

| 項目         | 記号                | 定格值                              | 単位 |

|------------|-------------------|----------------------------------|----|

| 電源電圧       | V <sub>DD</sub>   | V <sub>SS</sub> - 0.5 ~ + 6.0    | V  |

| 入力電圧       | $V_{IN}$          | $V_{SS} - 0.5 \sim V_{DD} + 0.5$ | V  |

| 出力電圧       | V <sub>out</sub>  | $V_{SS} - 0.5 \sim V_{DD} + 0.5$ | V  |

| 出力電流 1     | I <sub>out</sub>  | - 40 ~ + 40                      | mΑ |

| 保存温度       | T <sub>ST</sub>   | - 55 ~ + 125                     |    |

| オーバーシュート 2 | $V_{IO}$          | V <sub>DD</sub> + 1.0            | V  |

| アンダーシュート 2 | $V_{\mathrm{IU}}$ | V <sub>ss</sub> - 1.0            | V  |

- 1 1端子1秒間の場合。

- 2 50ns以内。

## 7.2. 推奨動作条件

表10.推奨動作条件

| 項目   | 記号              | 最小値   | 標準値 | 最大値 | 単位 |

|------|-----------------|-------|-----|-----|----|

| 電源電圧 | V <sub>DD</sub> | 4 . 5 | 5.0 | 5.5 | ٧  |

| 周囲温度 | Topr            | 0     | 25  | 70  |    |

### 7.3. 直流特性

表11.直流特性 <sup>1</sup>(V<sub>DD</sub> = 4.5~5.5V、V<sub>SS</sub> = 0V、T<sub>oor</sub> = 0~+70 )

| 27 <u> </u> |                   | o t t topi               | /               |                 |    |

|-------------|-------------------|--------------------------|-----------------|-----------------|----|

| 項目          | 記号                | 条件                       | 最小値             | 最大値             | 単位 |

| 高レベル入力電圧    | $V_{\mathrm{IH}}$ |                          | 2.4             | V <sub>DD</sub> | V  |

| 低レベル入力電圧    | $V_{IL}$          |                          | $V_{ss}$        | 0.7             | V  |

| 入力リーク電流     | $I_{LI}$          |                          | - 5             | 5               | μA |

| 高レベル出力電圧    | V <sub>oh</sub>   | $I_{OH} = -2mA$          | 3.6             | $V_{DD}$        | ٧  |

| 低レベル出力電圧    | V <sub>ol</sub>   | $I_{OL} = 3.2 \text{mA}$ | V <sub>ss</sub> | 0.5             | V  |

| 動作時消費電流 2   | $I_{DDO}$         | CLK = 1MHz               |                 | 1.2             | mΑ |

- 1  $I_{OH}$ は高レベル出力電流  $I_{OL}$ は低レベル出力電流を示します。

- 2 動作時消費電流はCLKの周波数にほぼ比例します。

## 7.4. 交流特性

表12.交流特性

| 項目                              | 記号    | 最小値         | 標準値 | 最大値                | 単位 |

|---------------------------------|-------|-------------|-----|--------------------|----|

| AD[3:0]セットアップ時間(to WRB )        | Tswa  | 2 9         |     |                    | ns |

| CSBセットアップ時間(to WRB )            | Tswc  | 2 9         |     |                    | ns |

| D[7:0]セットアップ時間(to WRB )         | Tswd  | 2 9         |     |                    | ns |

| AD[3:0]ホールド時間(to WRB )          | Thwa  | 5           |     |                    | ns |

| CSBホールド時間(to WRB )              | Thwc  | 5           |     |                    | ns |

| D[7:0] <b>ホールド時間</b> (to WRB )  | Thwd  | 5           |     |                    | ns |

| WRBローパルス幅                       | Twwr  | T c × 1     |     |                    | ns |

| WRBリカバリー時間                      | Trcw  | T c × 4     |     |                    | ns |

| AD[3:0]セットアップ時間(to RDB )        | Tsra  | 15          |     |                    | ns |

| CSBセットアップ時間(to RDB )            | Tsrc  | - (Tc×1-20) |     |                    | ns |

| AD[3:0]ホールド時間(to RDB )          | Thra  | 0           |     |                    | ns |

| CSBホールド時間(to RDB ) <sup>3</sup> | Thrc  | Tc×2+19     |     |                    | ns |

| RDBローパルス幅                       | Twrd  | T c × 3     |     |                    | ns |

| D[7:0]出力遅延時間(from RDB )         | Tdir  |             |     | 25                 | ns |

| D[7:0]出力遅延時間(from CSB )         | Tdic  |             |     | 25                 | ns |

| D[7:0]有効データアクセス時間(from RDB )    | Tdvr  |             |     | $Tc \times 2 + 20$ | ns |

| D[7:0]データフロート時間(from RDB )      | Tdfr  | 1           |     | 3 0                | ns |

| D[7:0]データフロート時間(from CSB )      | Tdfc  | 1           |     | 3 0                | ns |

| RDBリカバリー時間                      | Trcr  | T c × 2     |     |                    | ns |

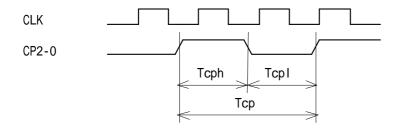

| CP2 - 0ハイパルス幅                   | Tcph  | Tc × 1 + 5  |     |                    | ns |

| CP2 - 0ローパルス幅                   | Tcpl  | Tc × 1 + 5  |     |                    | ns |

| CP2 - 0サイクル時間                   | Тср   | Tc×2+10     |     |                    | ns |

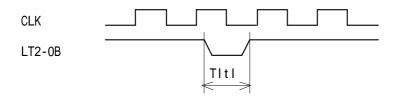

| LT2 - 0Bローパルス幅                  | Tltl  | 20          |     |                    | ns |

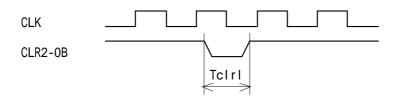

| CLR2 - 0Bロ <b>ーパル</b> ス幅        | Tclrl | 20          |     |                    | ns |

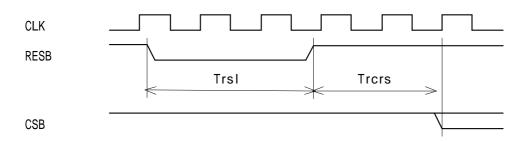

| RESBローパルス幅                      | Trsl  | T c × 2     |     |                    | ns |

| RESBUカバリー時間 <sup>4</sup>        | Trcrs | T c × 2     |     |                    | ns |

| CLKサイクル時間                       | Тc    | 29          |     |                    | ns |

| CLKハイパルス幅                       | Tch   | 1 4         |     |                    | ns |

| CLKローパルス幅                       | Tcl   | 1 4         |     |                    | ns |

<sup>3</sup> 本規定値は有効データがデータバスに出力される限界値を示します。実際のご使用にあたっては、接続するCPUの読み取りタイミング(交流特性)をご検討の上、CPUが余裕を持ってデータを読み取れるタイミングまでCSBをアサートしてください。

<sup>4</sup> リセット後のZEN0317Pに対する動作禁止時間。

### 7.5. タイミングダイアグラム

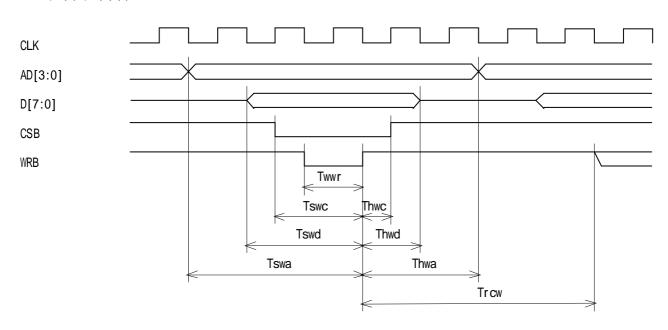

#### 7.5.1. **ライトサイクル**

図3.ライトサイクル

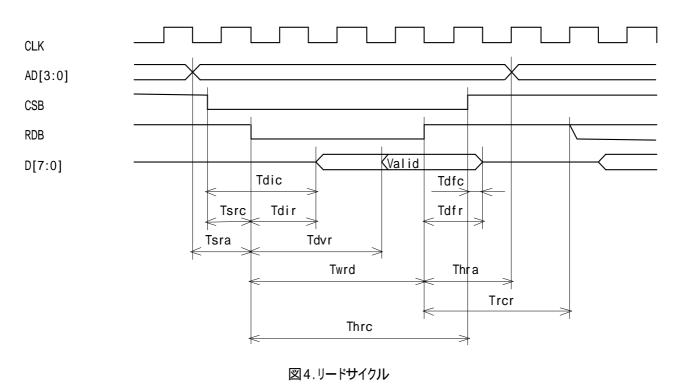

### 7.5.2. **リードサイクル**

#### 7.5.3. 外部カウントパルス入力

図5.外部カウントパルス入力

#### 7.5.4. 外部ラッチ入力

図6.外部ラッチ入力

#### 7.5.5. 外部クリア入力

図7.外部クリア入力

#### 7.5.6. リセット入力

図8.リセット入力

## 8. パッケージ形状

図9.外形寸法図(単位 mm)

# 9. 備考

# 10. 改訂履歴

| バージョン | 日付         | 内容     |

|-------|------------|--------|

| 1.0   | 2009/05/19 | 正式版発行。 |

|       |            |        |

|       |            |        |

|       |            |        |

#### ご注意

- (1)本製品および本資料は株式会社ジーニックの著作物です。

- (2)本資料に記載されております内容は工業所有権 その他の権利の実施に対する保証または実施権の許諾を 行うものではありません。

- (3)本資料に記載されております応用回路例は基本的な使用方法を示したものであり、回路の動作を保証するものではありません。

- (4)本製品の具体的な運用の結果、他への影響につきましては責任を負いかねますので、ご了承ください。

- (5)本製品は一般的な電子機器(電算機、計測機器、産業用ロボット、位置決め制御装置 etc.)に使用されることを前提にしております。したがって、人命に関わる輸送機器、医療機器、航空・宇宙、原子力関係機器などには使用しないでください。

株式会社 ジーニック

URL http://www.zenic.co.jp/ / E-mail support@zenic.co.jp 〒520 - 0801 滋賀県大津市におの浜4 - 7 - 5 オプテックスビル8F TEL:077 - 526 - 2101 / FAX:077 - 526 - 0500